LCD CONTROLLER S3C2440A RISC MICROPROCESSOR

15-14

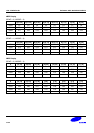

Timing Requirements

Image data should be transferred from the memory to the LCD driver using the VD[7:0] signal. VCLK signal is

used to clock the data into the LCD driver's shift register. After each horizontal line of data has been shifted into

the LCD driver's shift register, the VLINE signal is asserted to display the line on the panel.

The VM signal provides an AC signal for the display. The LCD uses the signal to alternate the polarity of the row

and column voltages, which are used to turn the pixels on and off, because the LCD plasma tends to deteriorate

whenever subjected to a DC voltage. It can be configured to toggle on every frame or to toggle every

programmable number of VLINE signals.

Figure 15-4 shows the timing requirements for the LCD driver interface.