S3C2440A RISC MICROPROCESSOR ARM INSTRUCTION SET

3-13

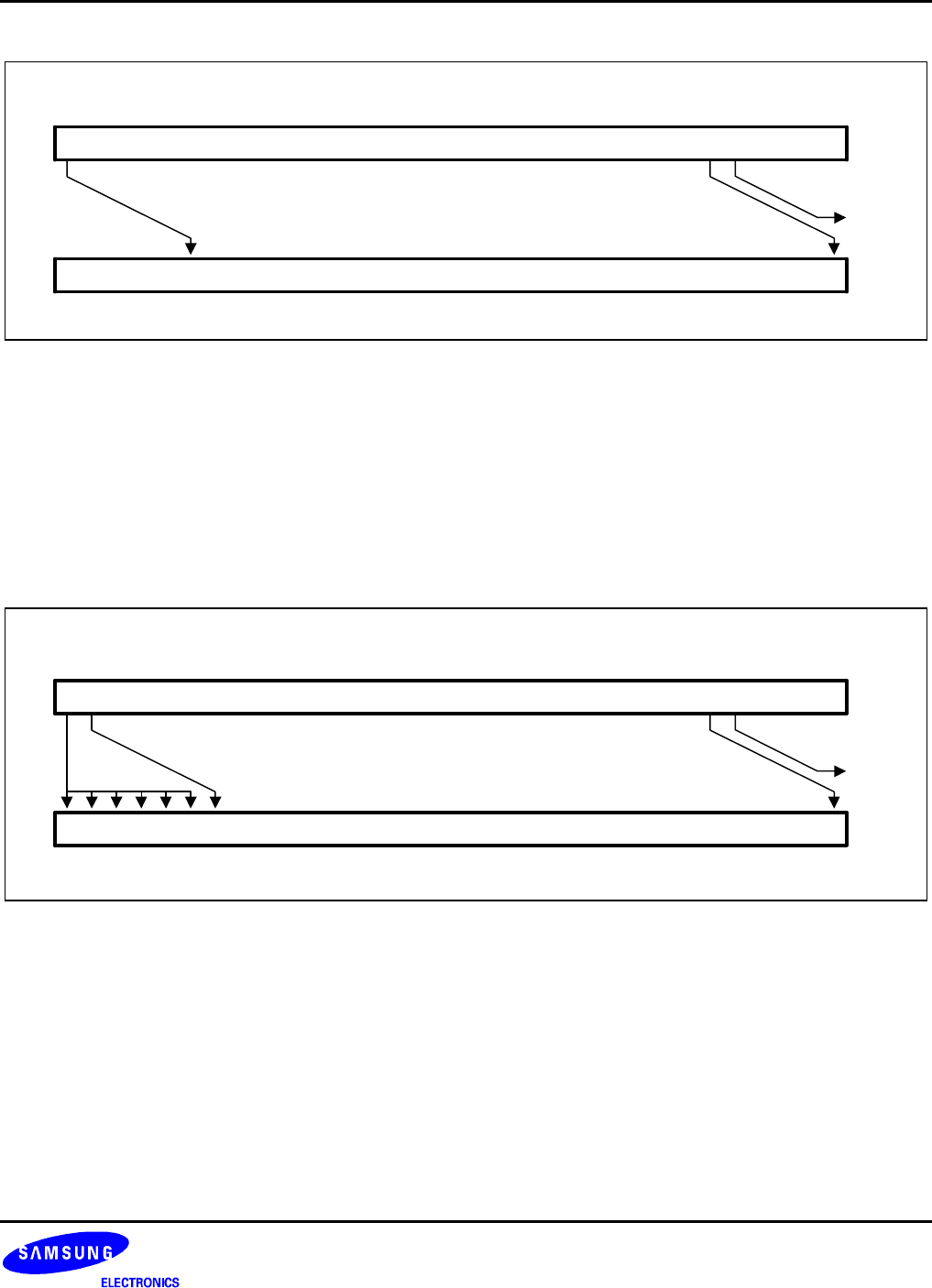

31

Contents of Rm

Value of Operand 2

0

carry out

45

00000

Figure 3-7. Logical Shift Right

The form of the shift field which might be expected to correspond to LSR #0 is used to encode LSR #32, which has

a zero result with bit 31 of Rm as the carry output. Logical shift right zero is redundant as it is the same as logical

shift left zero, so the assembler will convert LSR #0 (and ASR #0 and ROR #0) into LSL #0, and allow LSR #32 to

be specified.

An Arithmetic Shift Right (ASR) is similar to logical shift right, except that the high bits are filled with bit 31 of Rm

instead of zeros. This preserves the sign in 2's complement notation. For example, ASR #5 is shown in Figure

3-8.

31

Contents of Rm

Value of Operand 2

0

carry out

4530

Figure 3-8. Arithmetic Shift Right

The form of the shift field which might be expected to give ASR #0 is used to encode ASR #32. Bit 31 of Rm is

again used as the carry output, and each bit of operand 2 is also equal to bit 31 of Rm. The result is therefore all

ones or all zeros, according to the value of bit 31 of Rm.