THUMB INSTRUCTION SET S3C2440A RISC MICROPROCESSOR

4-14

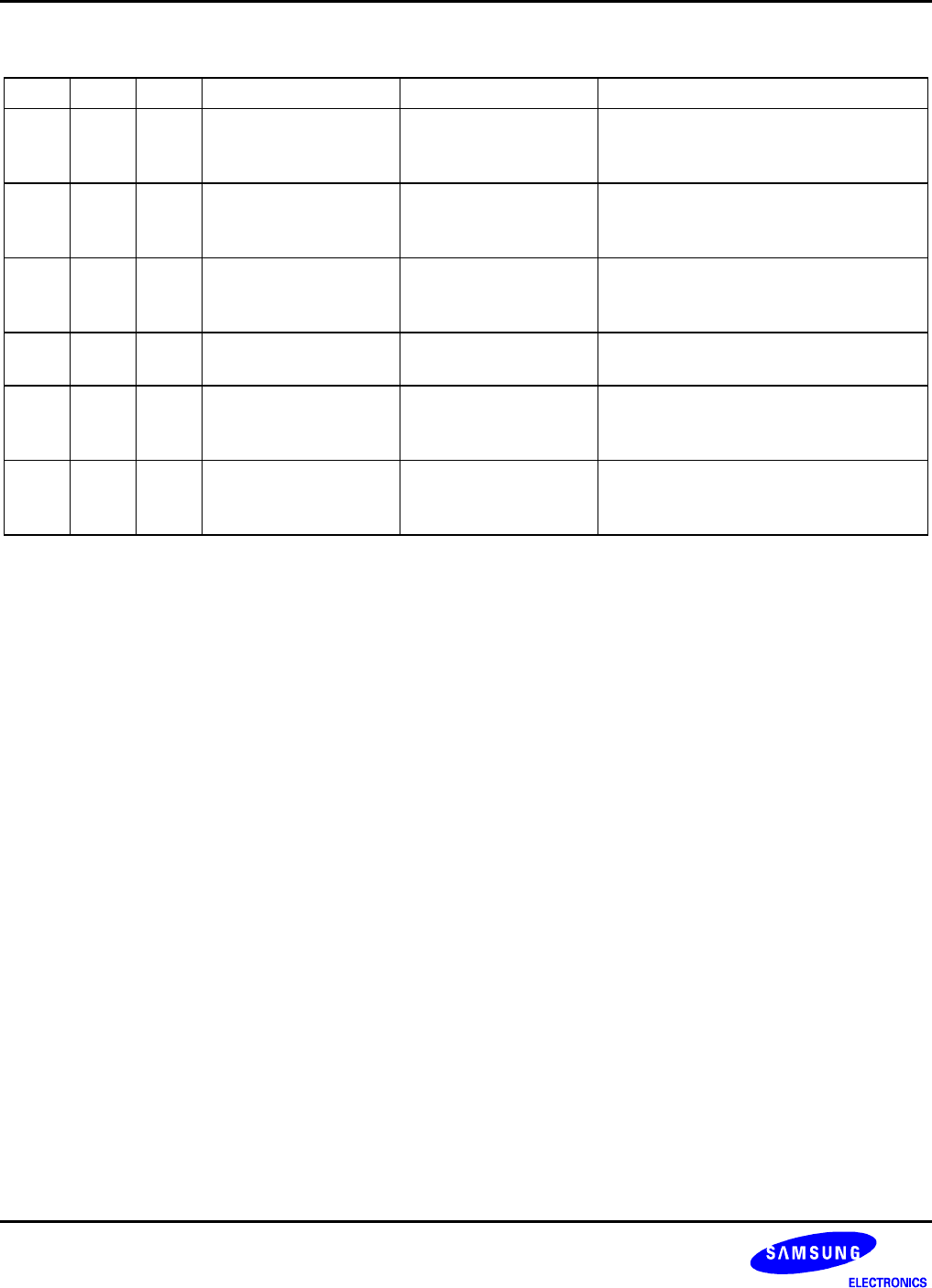

Table 4-6. Summary of Format 5 Instructions (Continued)

Op H1 H2 THUMB assembler ARM equivalent Description

01 1 1 CMP Hd, Hs CMP Hd, Hs Compare two registers in the range

8-15. Set the condition code flags on

the result.

10 0 1 MOV Rd, Hs MOV Rd, Hs Move a value from a register in the

range 8-15 to a register in the range 0-

7.

10 1 0 MOV Hd, Rs MOV Hd, Rs Move a value from a register in the

range 0-7 to a register in the range

8-15.

10 1 1 MOV Hd, Hs MOV Hd, Hs Move a value between two registers in

the range 8-15.

11 0 0 BX Rs BX Rs Perform branch (plus optional state

change) to address in a register in the

range 0-7.

11 0 1 BX Hs BX Hs Perform branch (plus optional state

change) to address in a register in the

range 8-15.

INSTRUCTION CYCLE TIMES

All instructions in this format have an equivalent ARM instruction as shown in Table 4-6. The instruction cycle

times for the THUMB instruction are identical to that of the equivalent ARM instruction.

THE BX INSTRUCTION

BX performs a Branch to a routine whose start address is specified in a Lo or Hi register.

Bit 0 of the address determines the processor state on entry to the routine:

Bit 0 = 0 Causes the processor to enter ARM state.

Bit 0 = 1 Causes the processor to enter THUMB state.

NOTE

The action of H1 = 1 for this instruction is undefined, and should not be used.