ARM INSTRUCTION SET S3C2440A RISC MICROPROCESSOR

3-16

IMMEDIATE OPERAND ROTATES

The immediate operand rotate field is a 4 bit unsigned integer which specifies a shift operation on the 8 bit

immediate value. This value is zero extended to 32 bits, and then subject to a rotate right by twice the value in the

rotate field. This enables many common constants to be generated, for example all powers of 2.

WRITING TO R15

When Rd is a register other than R15, the condition code flags in the CPSR may be updated from the ALU flags as

described above.

When Rd is R15 and the S flag in the instruction is not set the result of the operation is placed in R15 and the

CPSR is unaffected.

When Rd is R15 and the S flag is set the result of the operation is placed in R15 and the SPSR corresponding to

the current mode is moved to the CPSR. This allows state changes which automatically restore both PC and

CPSR. This form of instruction should not be used in User mode.

USING R15 AS AN OPERANDY

If R15 (the PC) is used as an operand in a data processing instruction the register is used directly.

The PC value will be the address of the instruction, plus 8 or 12 bytes due to instruction prefetching. If the shift

amount is specified in the instruction, the PC will be 8 bytes ahead. If a register is used to specify the shift amount

the PC will be 12 bytes ahead.

TEQ, TST, CMP AND CMN OPCODES

NOTES

TEQ, TST, CMP and CMN do not write the result of their operation but do set flags in the CPSR. An

assembler should always set the S flag for these instructions even if this is not specified in the mnemonic.

The TEQP form of the TEQ instruction used in earlier ARM processors must not be used: the PSR transfer

operations should be used instead.

The action of TEQP in the ARM920T is to move SPSR_<mode> to the CPSR if the processor is in a privileged

mode and to do nothing if in User mode.

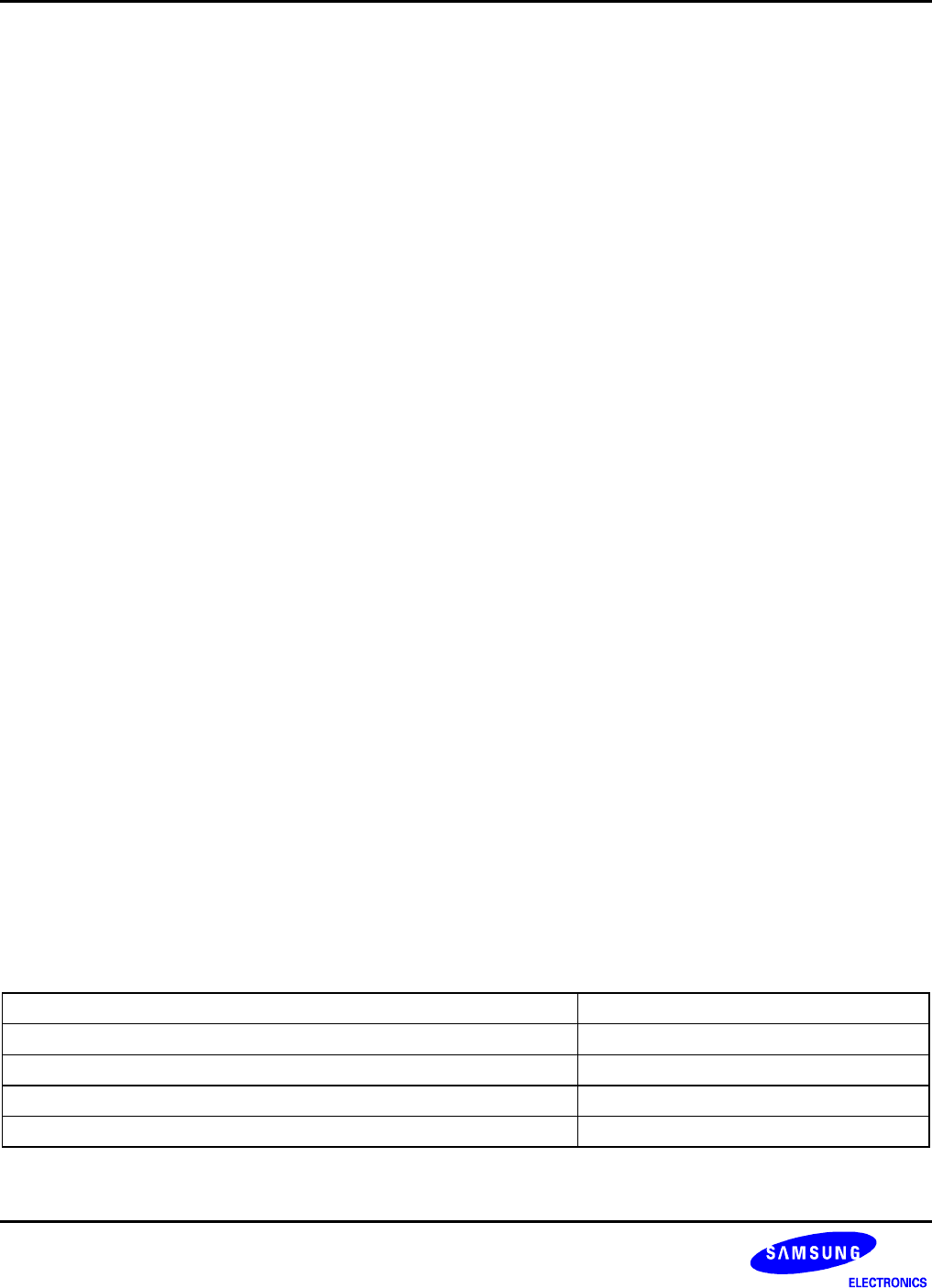

INSTRUCTION CYCLE TIMES

Data Processing instructions vary in the number of incremental cycles taken as follows:

Table 3-4. Incremental Cycle Times

Processing Type Cycles

Normal data processing 1S

Data processing with register specified shift 1S + 1I

Data processing with PC written 2S + 1N

Data processing with register specified shift and PC written 2S + 1N +1I

NOTE: S, N and I are as defined sequential (S-cycle), non-sequential (N-cycle), and internal (I-cycle) respectively.