S3C2440A RISC MICROPROCESSOR CAMERA INTERFACE

23-3

TIMING DIAGRAM

jht}zuj

jht}zujjht}zuj

jht}zuj

j j j j j

jhtoylm

jhtoylmjhtoylm

jhtoylm

jhtoylmG

jhtoylmGjhtoylmG

jhtoylmG

OXoP

OXoPOXoP

OXoP

jhtwjsr

jhtwjsrjhtwjsr

jhtwjsr

jhtkh{h

jhtkh{hjhtkh{h

jhtkh{h

^aW

^aW^aW

^aW

}G

}G}G

}G

o¡G

o¡Go¡G

o¡G

XG

XGXG

XG

_TG

_TG_TG

_TG

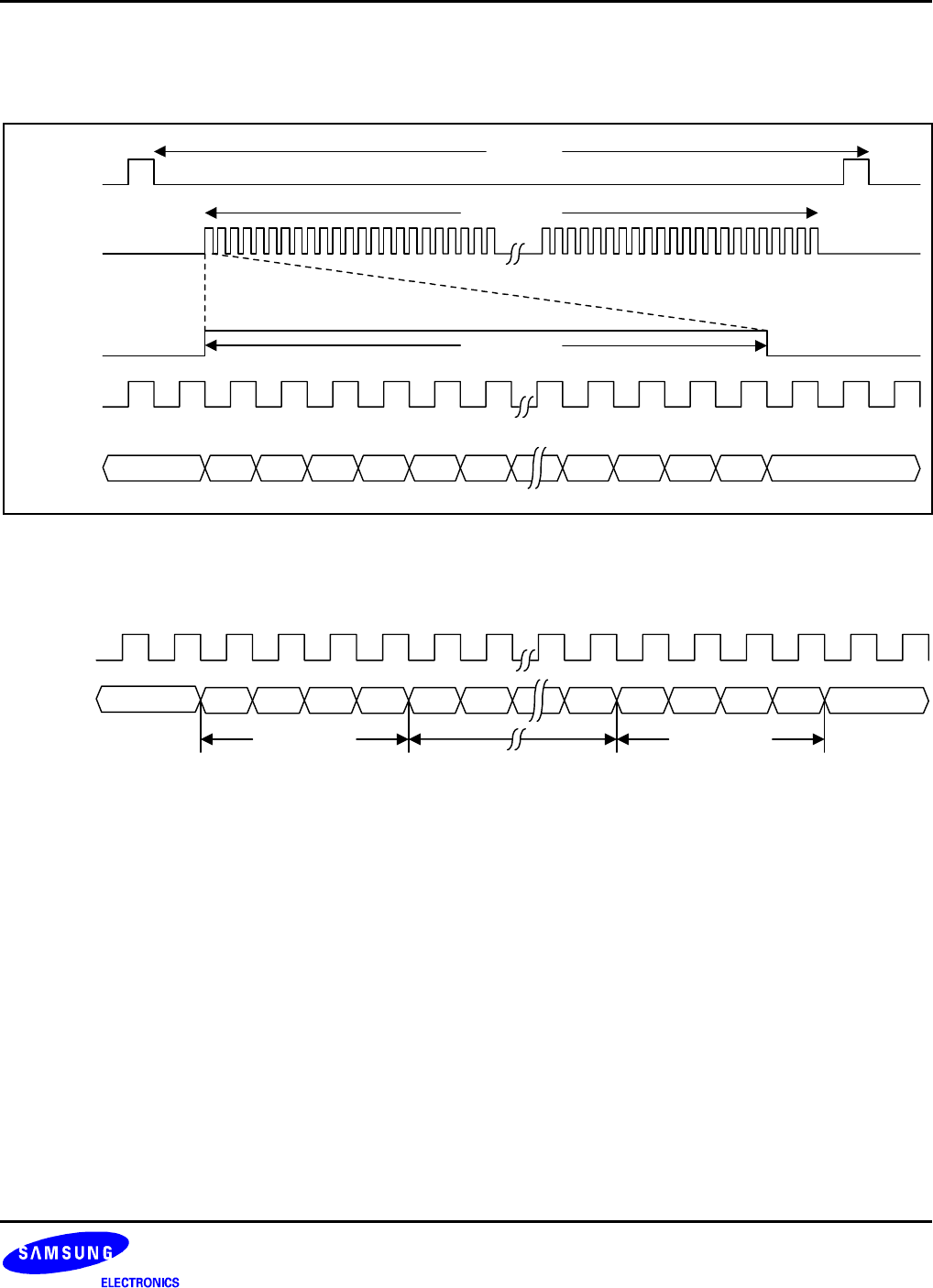

Figure 23-2 ITU-R BT 601 Input Timing Diagram

jhtwjsr

jhtwjsrjhtwjsr

jhtwjsr

jhtkh{h

jhtkh{hjhtkh{h

jhtkh{h

^aW

^aW^aW

^aW

j

mm

mmmm

mm WW

WWWW

WW WW

WWWW

WW

j

mm

mmmm

mm WW

WWWW

WW WW

WWWW

WW

}G

}G}G

}G

G

GG

G

wG

wGwG

wG

}G

}G}G

}G

G

GG

G

Figure 23-3 ITU-R BT 656 Input Timing Diagram

There are two timing reference signals in ITU-R BT 656 format, one is at the beginning of each video data block

(start of active video, SAV) and other is at the end of each video data block (end of active video, EAV) as shown in

Figure 23-3 and Table 23-2.