S3C2440A RISC MICROPROCESSOR CLOCK & POWER MANAGEMENT

7-17

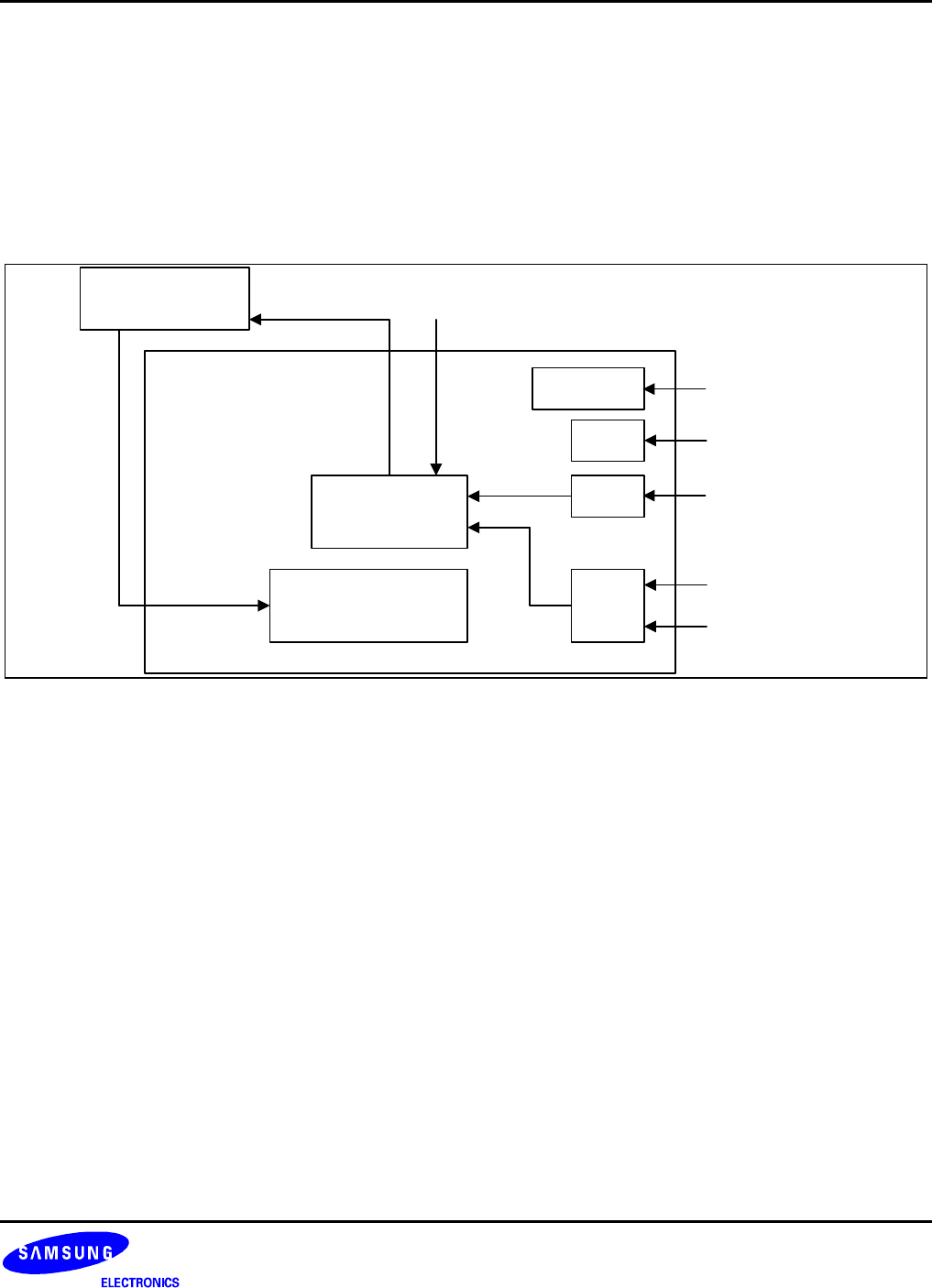

Power Control of VDDi and VDDiarm

In SLEEP mode, VDDi, VDDiarm, VDDMPLL and VDDUPLL will be turned off, which is controlled by PWREN pin.

If PWREN signal is activated(H), VDDi and VDDiarm are supplied by an external voltage regulator. If PWREN pin

is inactive (L), the VDDi and VDDiarm are turned off.

NOTE

Although VDDi, VDDiarm, VDDMPLL and VDDUPLL may be turned off, the other power pins have to be supplied.

S3C2440X

Power CTRL

(Alive Block)

RTC Alarm

EINT

External Interrupt

3.3V Power

PWREN

VDDi

VDDiarm

VDDMPLL

VDDUPLL

Core & Peripherals

RTC

I/O

Regulator

1.2V/1.3V

EN

1.2V/1.3V

Power

VDDalive

ADC

1.8V~3.6V

Memory

Interface

1.8V/2.5V/3.3V

3.3V

Figure 7-12. SLEEP Mode

NOTE

During sleep mode, if you don’t use Touch Screen panel, Touch ports (XP, XM, YP, and YM) must be floating.

That is, Touch ports (XP, XM, YP, and YM) shouldn’t be connected to GND sources. Because XP,YP will be

maintained H during sleep mode.