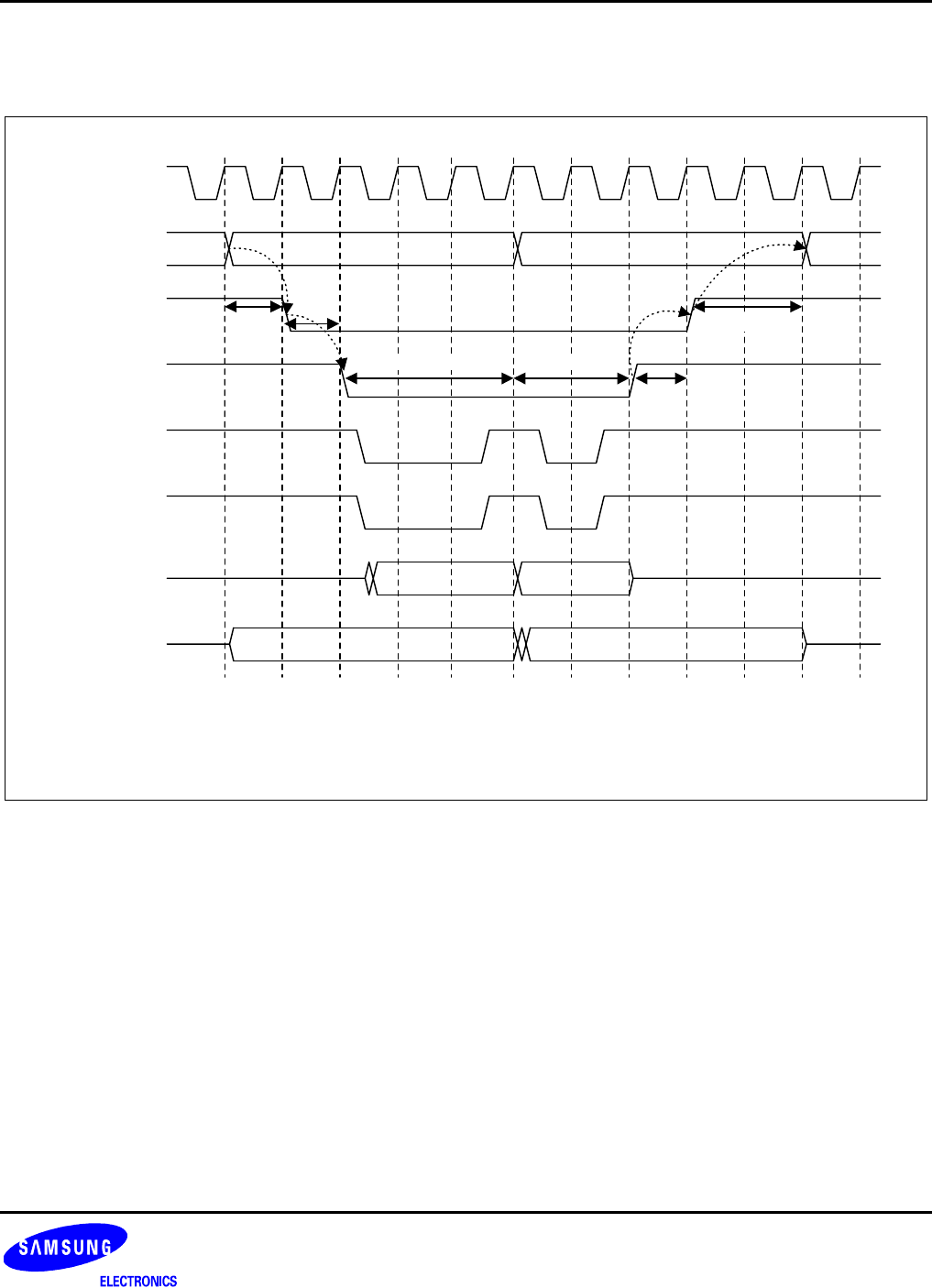

S3C2440A RISC MICROPROCESSOR MEMORY CONTROLLER

DEC.13, 2002

5-11

PROGRAMMABLE ACCESS CYCLE

Tcoh

Tcos

Tacs

HCLK

A[24:0]

nGCS

nOE

nWE

nWBE

D[31:0](R)

D[31:0] (W)

Tacc Tacp

Tcah

Tacs = 1 cycle

Tcos = 1 cycle

Tacc = 3 cycles

Tacp = 2 cycles

Tcoh = 1 cycle

Tcah = 2 cycles

Figure 5-12. S3C2440A nGCS Timing Diagram