S3C2440A RISC MICROPROCESSOR CAMERA INTERFACE

23-19

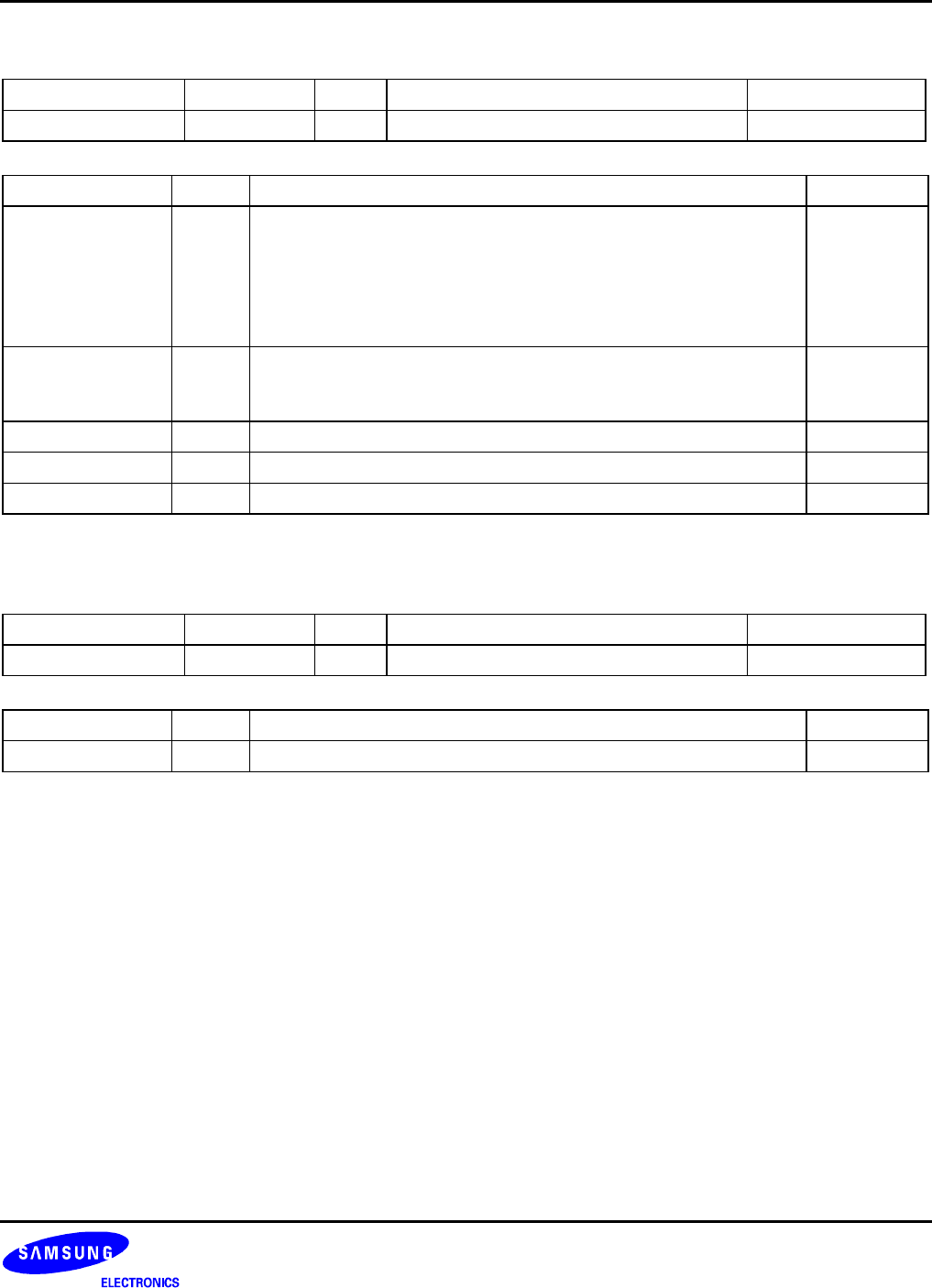

CODEC MAIN-SCALER CONTROL REGISTER

Register Address R/W Description Reset Value

CICOSCCTRL 0x4F000058 RW Codec main-scaler control 0

CICOSCCTRL Bit Description Initial State

ScalerBypass_Co [31]

Codec scaler bypass for upper 2048 x 2048 size (In this case,

ImgCptEn_CoSC and ImgCptEn_PrSC should be 0, but ImgCptEn

should be 1. It is not allowed to capture preview image. This mode

is intended to capture JPEG input image for DSC application) In

this case, input pixel buffering depends on only input FIFOs, so the

system bus should be not busy in this mode.

0

ScaleUpDown_Co [30:29]

Scale up/down flag for codec scaler

(In 1:1 scale ratio, this bit should be “1”)

00 = down 11 = up

00

MainHorRatio_Co [24:16] Horizontal scale ratio for codec main-scaler 0

CoScalerStart [15] Codec scaler start 0

MainVerRatio_Co [8:0] Vertical scale ratio for codec main-scaler 0

CODEC DMA TARGET AREA REGISTER

Register Address R/W Description Reset Value

CICOTAREA 0x4F00005C RW Codec scaler target area 0

CICOTAREA Bit Description Initial State

CICOTAREA [25:0] Target area for codec DMA = Target H size x Target V size 0