S3C2440A RISC MICROPROCESSOR PROGRAMMER'S MODEL

2-7

Accessing Hi-Registers in THUMB State

In THUMB state, registers R8-R15 (“Hi registers”) are not part of the standard register set. However, the

assembly language programmer has limited access to them, and can use them for fast temporary storage.

A value may be transferred from a register in the range R0-R7 (a Lo register) to a Hi register and from a Hi register

to a Lo register, using special variants of the MOV instruction. Hi register values can also be compared against or

added to Lo register values with the CMP and ADD instructions. For more information, Please refer to Figure 3-34.

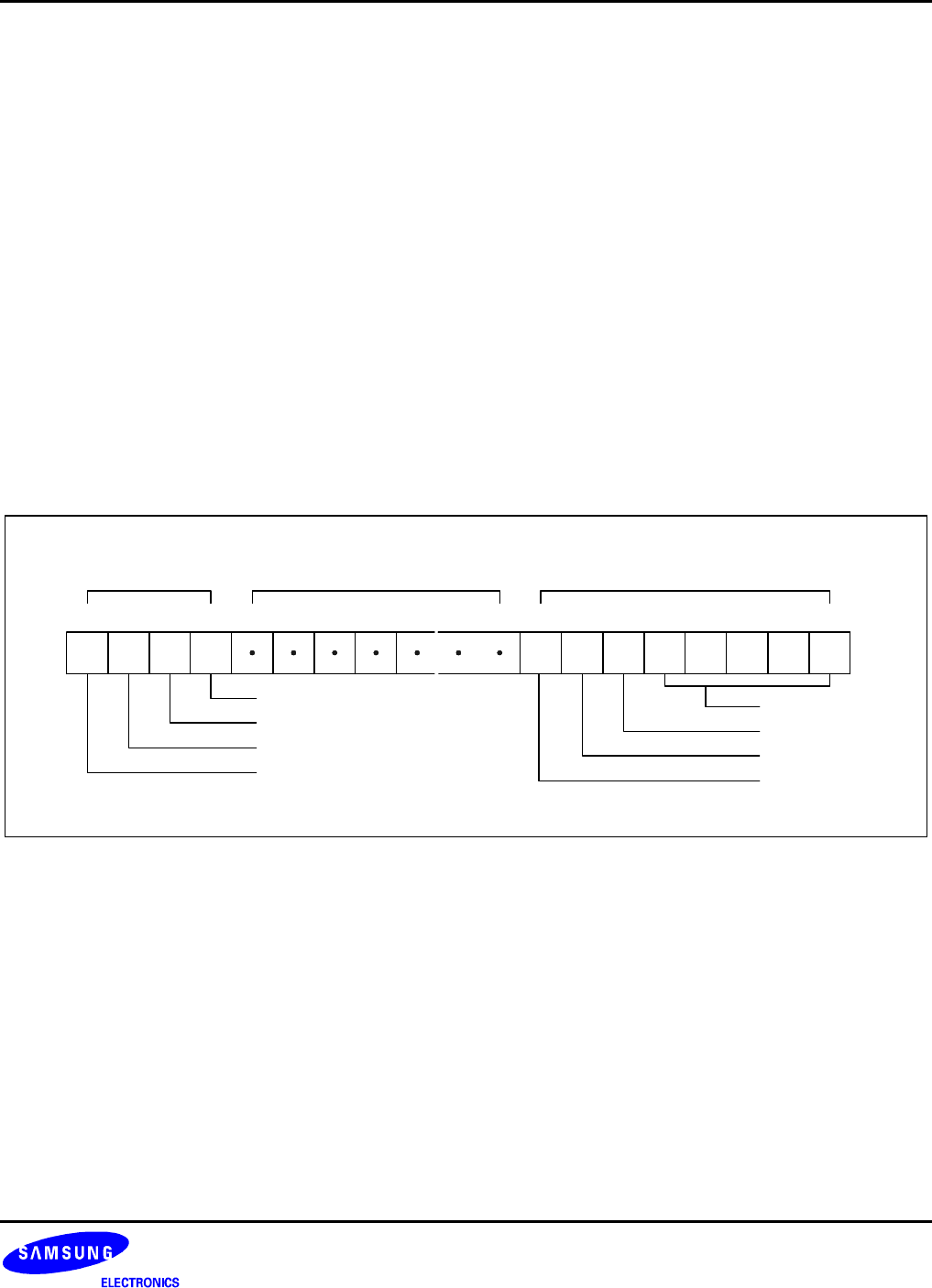

THE PROGRAM STATUS REGISTERS

The ARM920T contains a Current Program Status Register (CPSR), plus five Saved Program Status Registers

(SPSRs) for use by exception handlers. These register's functions are:

• Hold information about the most recently performed ALU operation

• Control the enabling and disabling of interrupts

• Set the processor operating mode

The arrangement of bits is shown in Figure 2-6.

31

Condition Code Flags

Overflow

N

Z C V I F T M4 M3 M2 M1 M0

30 29 2728 26252423 876543210

(Reserved) Control Bits

Carry/Borrow/Extend

Zero

Negative/Less Than

Mode bits

State bit

FIQ disable

IRQ disable

~

~

~

~

Figure 2-6. Program Status Register Format