S3C2440A RISC MICROPROCESSOR THUMB INSTRUCTION SET

4-39

INSTRUCTION CYCLE TIMES

This instruction format does not have an equivalent ARM instruction.

Table 4-20. The BL Instruction

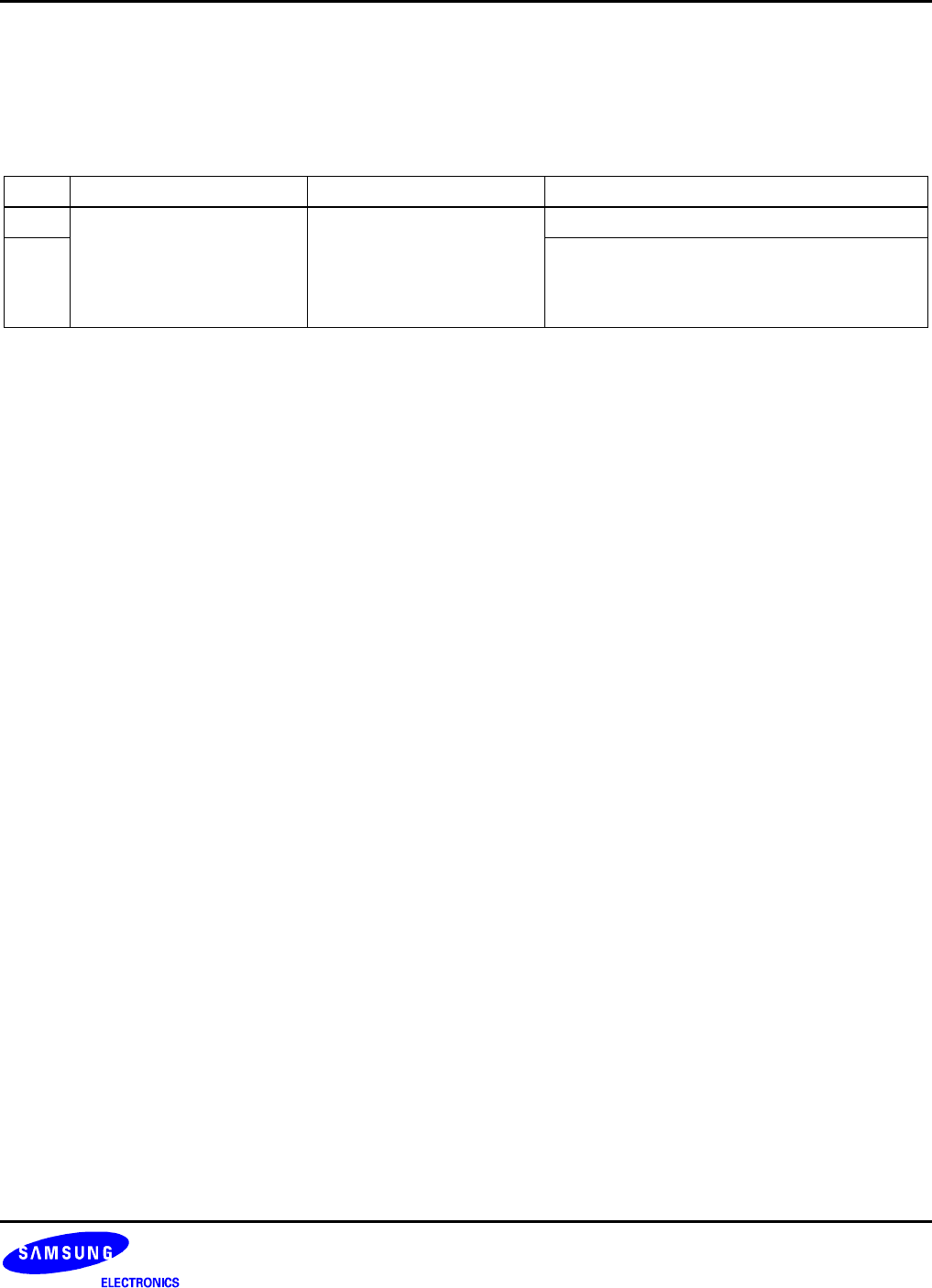

L THUMB assembler ARM equivalent Description

0 BL label none LR := PC + OffsetHigh << 12

1 temp := next instruction address

PC := LR + OffsetLow << 1

LR := temp | 1

EXAMPLES

BL faraway ; Unconditionally Branch to 'faraway'

next

• and place following instruction

• address, ie "next", in R14,the Link register and

set bit 0 of LR high.

Note that the THUMB opcodes will contain the

number of halfwords to offset.

faraway

• ; Must be Half-word aligned.

•