IIS-BUS INTERFACE S3C2440A RISC MICROPROCESSOR

21-8

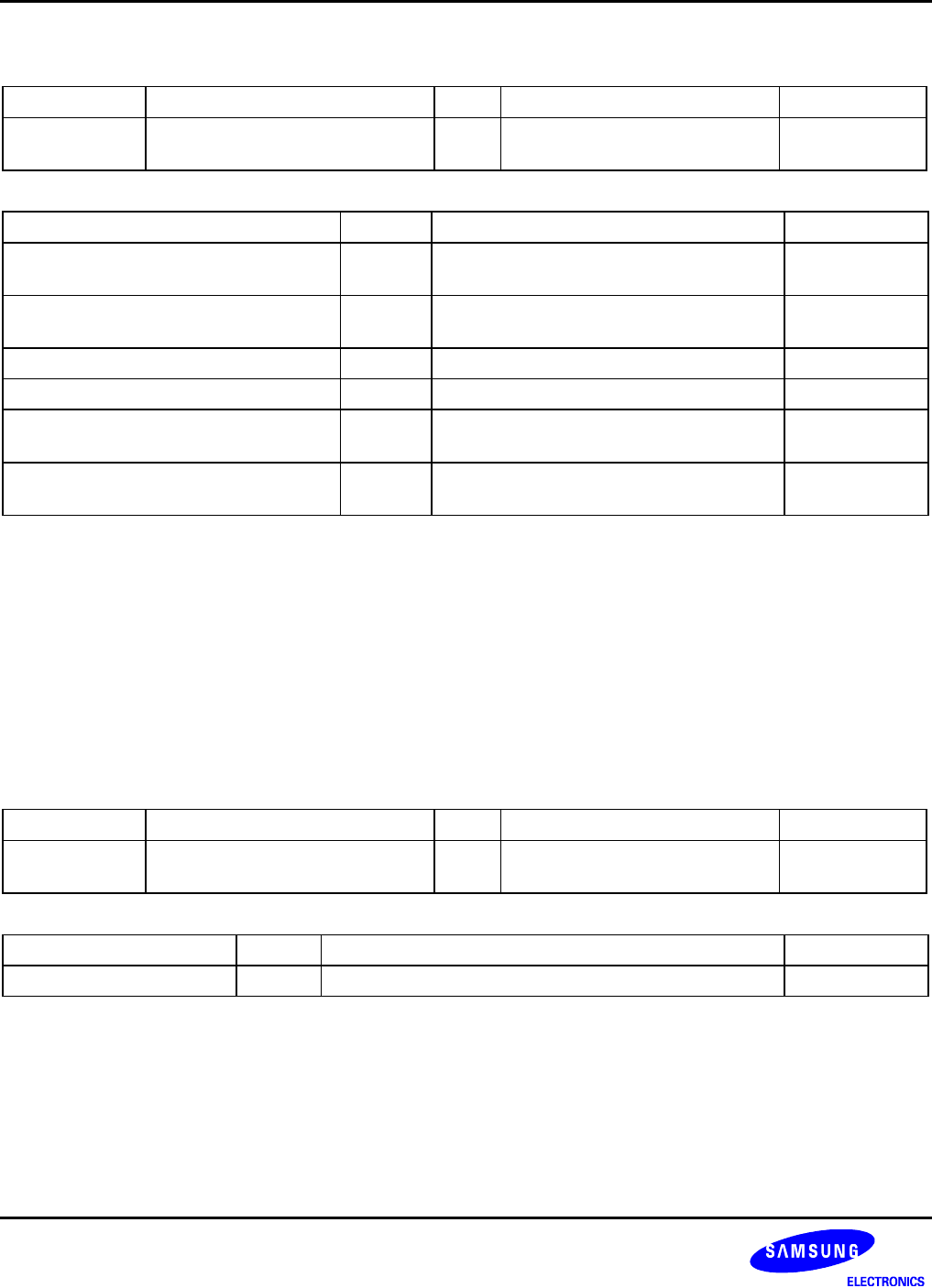

IIS FIFO CONTROL (IISFCON) REGISTER

Register Address R/W Description Reset Value

IISFCON 0x5500000C (Li/HW, Li/W, Bi/W)

0x5500000E (Bi/HW)

R/W IIS FIFO interface register 0x0

IISFCON Bit Description Initial State

Transmit FIFO access mode select [15] 0 = Normal

1 = DMA

0

Receive FIFO access mode select [14] 0 = Normal

1 = DMA

0

Transmit FIFO [13] 0 = Disable 1 = Enable 0

Receive FIFO [12] 0 = Disable 1 = Enable 0

Transmit FIFO data count

(Read only)

[11:6] Data count value = 0 ~ 32 000000

Receive FIFO data count

(Read only)

[5:0] Data count value = 0 ~ 32 000000

NOTES:

1. The IISFCON register is accessible for each halfword and word unit using STRH/STR and LDRH/LDR instructions or

short

int/int type pointer in Little/Big endian mode.

2. (Li/HW/W): Little/HalfWord/Word.

(Bi/HW/W): Big/HalfWord/Word.

IIS FIFO (IISFIFO) REGISTER

IIS bus interface contains two 64-byte FIFO for the transmit and receive mode. Each FIFO has 16-width and 32-

depth form, which allows the FIFO to handles data for each halfword unit regardless of valid data size. Transmit

and receive FIFO access is performed through FIFO entry; the address of FENTRY is 0x55000010.

Register Address R/W Description Reset Value

IISFIFO 0x55000010(Li/HW)

0x55000012(Bi/HW)

R/W IIS FIFO register 0x0

IISFIF Bit Description Initial State

FENTRY [15:0] Transmit/Receive data for IIS 0x0

NOTES:

1. The IISFIFO register is accessible for each halfword and word unit using STRH and LDRH instructions or short int type

pointer in Little/Big endian mode.

2. (Li/HW): Little/HalfWord.

(Bi/HW): Big/HalfWord.