S3C2440A RISC MICROPROCESSOR PWM TIMER

10-3

PWM TIMER OPERATION

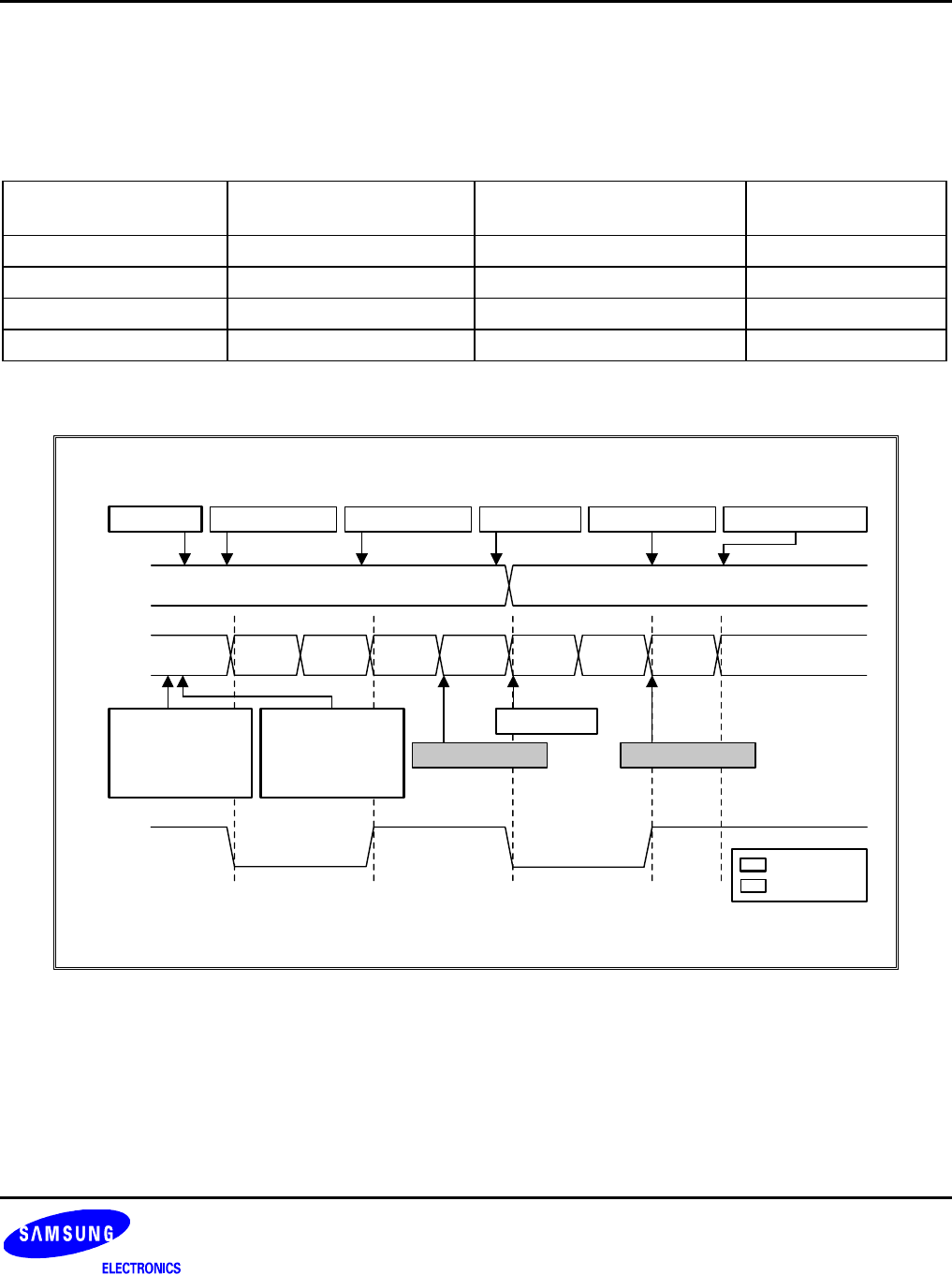

PRESCALER & DIVIDER

An 8-bit prescaler and a 4-bit divider make the following output frequencies:

4-bit divider settings Minimum resolution

(prescaler = 0)

Maximum resolution

(prescaler = 255)

Maximum interval

(TCNTBn = 65535)

1/2 (PCLK = 50 MHz) 0.0400 us (25.0000 MHz) 10.2400 us (97.6562 KHz) 0.6710 sec

1/4 (PCLK = 50 MHz) 0.0800 us (12.5000 MHz) 20.4800 us (48.8281 KHz) 1.3421 sec

1/8 (PCLK = 50 MHz) 0.1600 us ( 6.2500 MHz) 40.9601 us (24.4140 KHz) 2.6843 sec

1/16 (PCLK = 50 MHz) 0.3200 us ( 3.1250 MHz) 81.9188 us (12.2070 KHz) 5.3686 sec

BASIC TIMER OPERATION

TCMPn

1 0

TCNTn

3 3 2 1 0 2 1 0 0

Start bit=1 Timer is started TCNTn=TCMPn Auto-reload TCNTn=TCMPn Timer is stopped

TOUTn

Command

Status

TCNTBn=3

TCNTBn=1

Manual update=1

Auto-reload=1

TCNTBn=2

TCNTBn=0

Manual update=0

Auto-reload=1

Interrupt request

Auto-reload

Interrupt request

Figure 10-2. Timer Operations

A timer (except the timer ch-5) has TCNTBn, TCNTn, TCMPBn and TCMPn. (TCNTn and TCMPn are the names

of the internal registers. The TCNTn register can be read from the TCNTOn register) The TCNTBn and the

TCMPBn are loaded into the TCNTn and the TCMPn when the timer reaches 0. When the TCNTn reaches 0, an

interrupt request will occur if the interrupt is enabled.