INTERRUPT CONTROLLER S3C2440A RISC MICROPROCESSOR

14-14

INTERRUPT PENDING (INTPND) REGISTER

Each of the 32 bits in the interrupt pending register shows whether the corresponding interrupt request, which is

unmasked and waits for the interrupt to be serviced, has the highest priority . Since the INTPND register is located

after the priority logic, only one bit can be set to 1, and that interrupt request generates IRQ to CPU. In interrupt

service routine for IRQ, you can read this register to determine which interrupt source is serviced among the 32

sources.

Like the SRCPND register, this register has to be cleared in the interrupt service routine after clearing the

SRCPND register. We can clear a specific bit of the INTPND register by writing a data to this register. It clears only

the bit positions of the INTPND register corresponding to those set to one in the data. The bit positions

corresponding to those that are set to 0 in the data remains as they are.

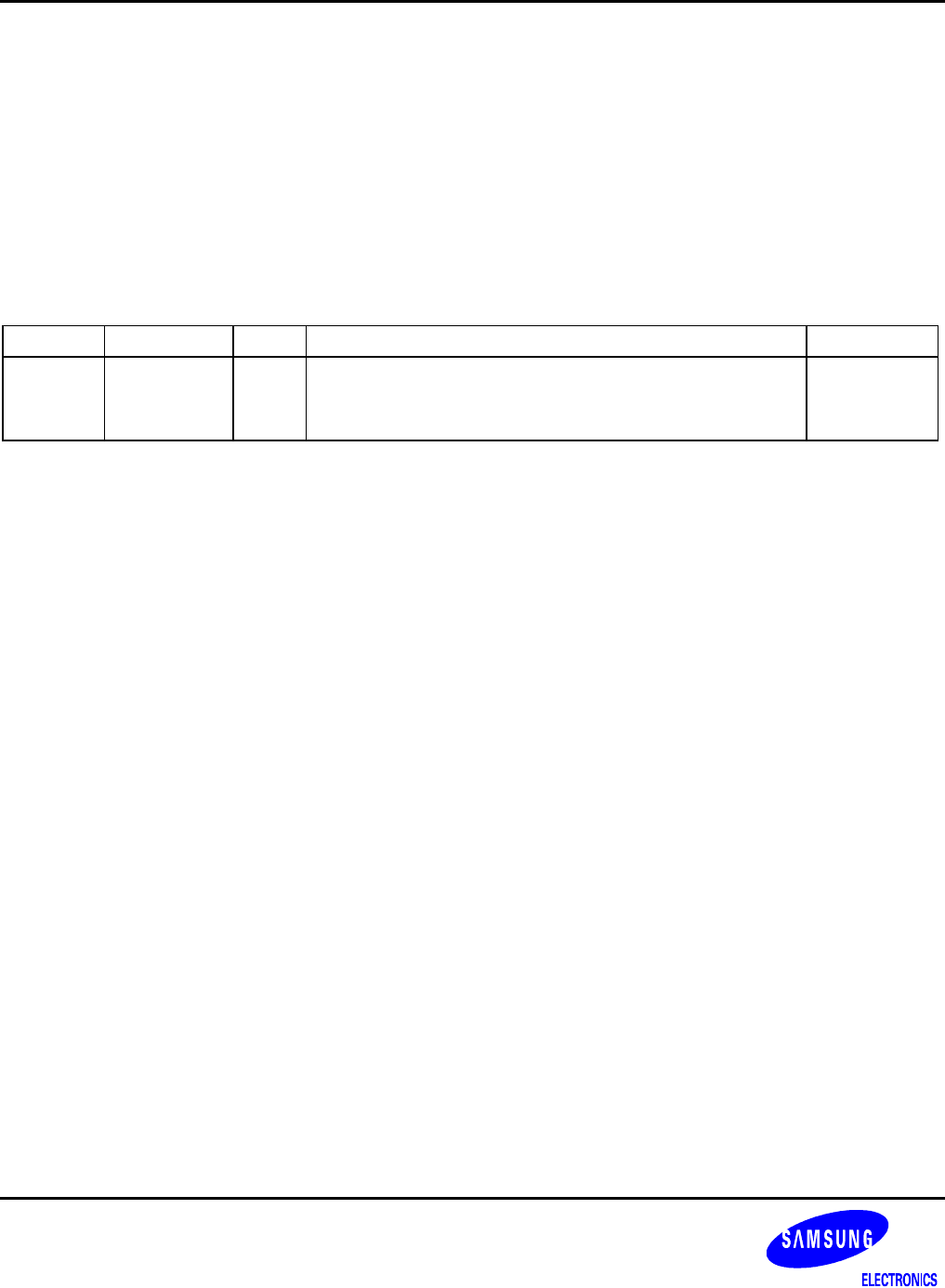

Register Address R/W Description Reset Value

INTPND 0X4A000010 R/W Indicate the interrupt request status.

0 = The interrupt has not been requested.

1 = The interrupt source has asserted the interrupt request.

0x00000000

Note

If the FIQ mode interrupt occurs, the corresponding bit of INTPND will not be turned on as the INTPND register is

available only for IRQ mode interrupt.