S3C2440A RISC MICROPROCESSOR DMA

8-9

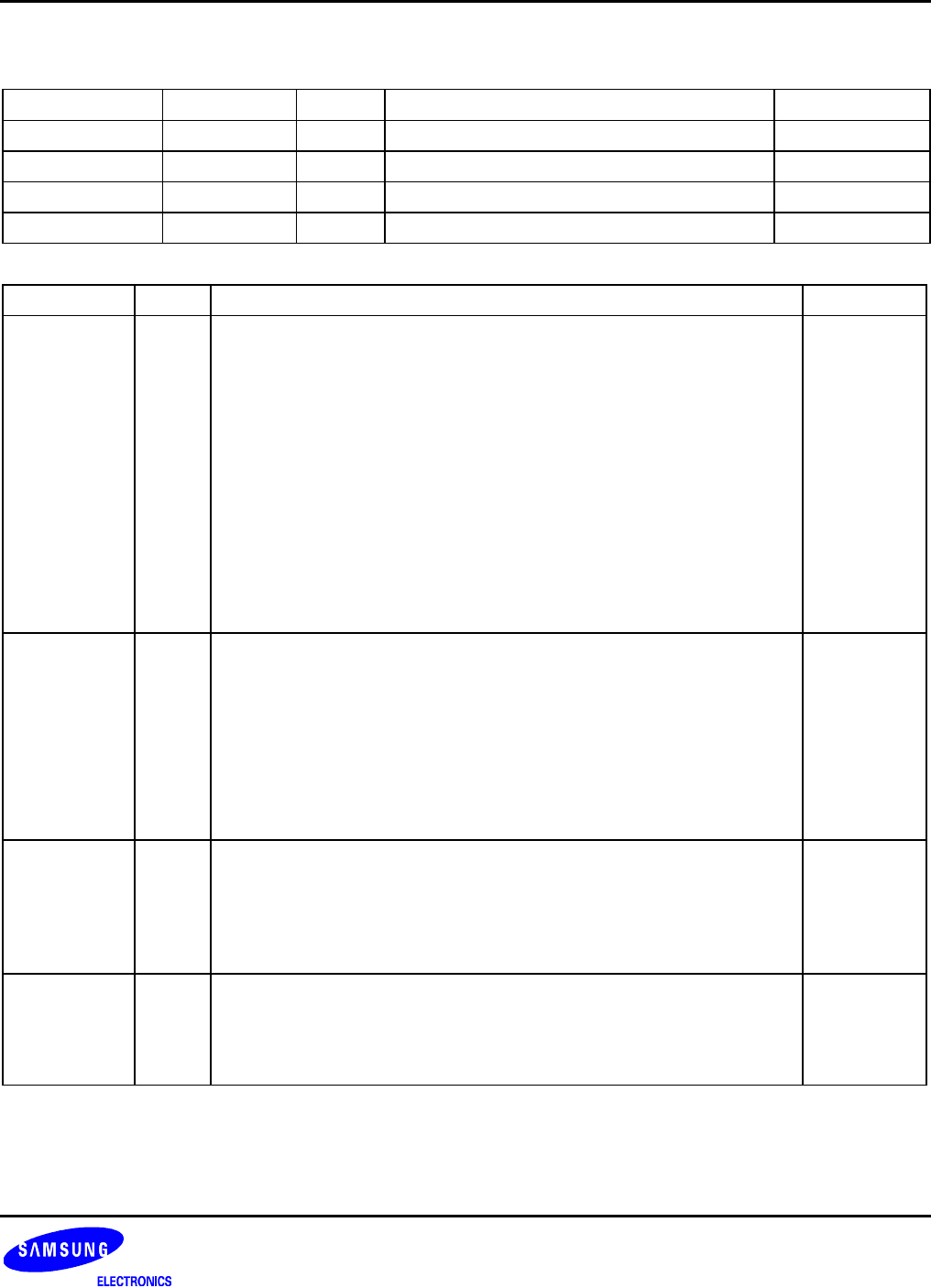

DMA CONTROL (DCON) REGISTER

Register Address R/W Description Reset Value

DCON0 0x4B000010 R/W DMA 0 control register 0x00000000

DCON1 0x4B000050 R/W DMA 1 control register 0x00000000

DCON2 0x4B000090 R/W DMA 2 control register 0x00000000

DCON3 0x4B0000D0 R/W DMA 3 control register 0x00000000

DCONn Bit Description Initial State

DMD_HS [31] Select one between Demand mode and Handshake mode.

0: Demand mode will be selected.

1: Handshake mode will be selected.

In both modes, DMA controller starts its transfer and asserts DACK for

a given asserted DREQ. The difference between the two modes is

whether it waits for the de-asserted DACK or not. In the Handshake

mode, DMA controller waits for the de-asserted DREQ before starting

a new transfer. If it finds the de-asserted DREQ, it de-asserts DACK

and waits for another asserted DREQ. In contrast, in the Demand

mode, DMA controller does not wait until the DREQ is de-asserted. It

just de-asserts DACK and then starts another transfer if DREQ is

asserted. We recommend using Handshake mode for external DMA

request sources to prevent unintended starts of new transfers.

0

SYNC [30] Select DREQ/DACK synchronization.

0: DREQ and DACK are synchronized to PCLK (APB clock).

1: DREQ and DACK are synchronized to HCLK (AHB clock).

Therefore, for devices attached to AHB system bus, this bit has to be

set to 1, while for those attached to APB system, it should be set to 0.

For the devices attached to external systems, the user should select

this bit depending on which the external system is synchronized with

between AHB system and APB system.

0

INT [29] Enable/Disable the interrupt setting for CURR_TC (terminal count)

0: CURR_TC interrupt is disabled. The user has to view the transfer

count in the status register (i.e. polling).

1: interrupt request is generated when all the transfer is done (i.e.

CURR_TC becomes 0).

0

TSZ [28] Select the transfer size of an atomic transfer (i.e. transfer performed

each time DMA owns the bus before releasing the bus).

0: a unit transfer is performed.

1: a burst transfer of length four is performed.

0