S3C2440A RISC MICROPROCESSOR IIC-BUS INTERFACE

20-9

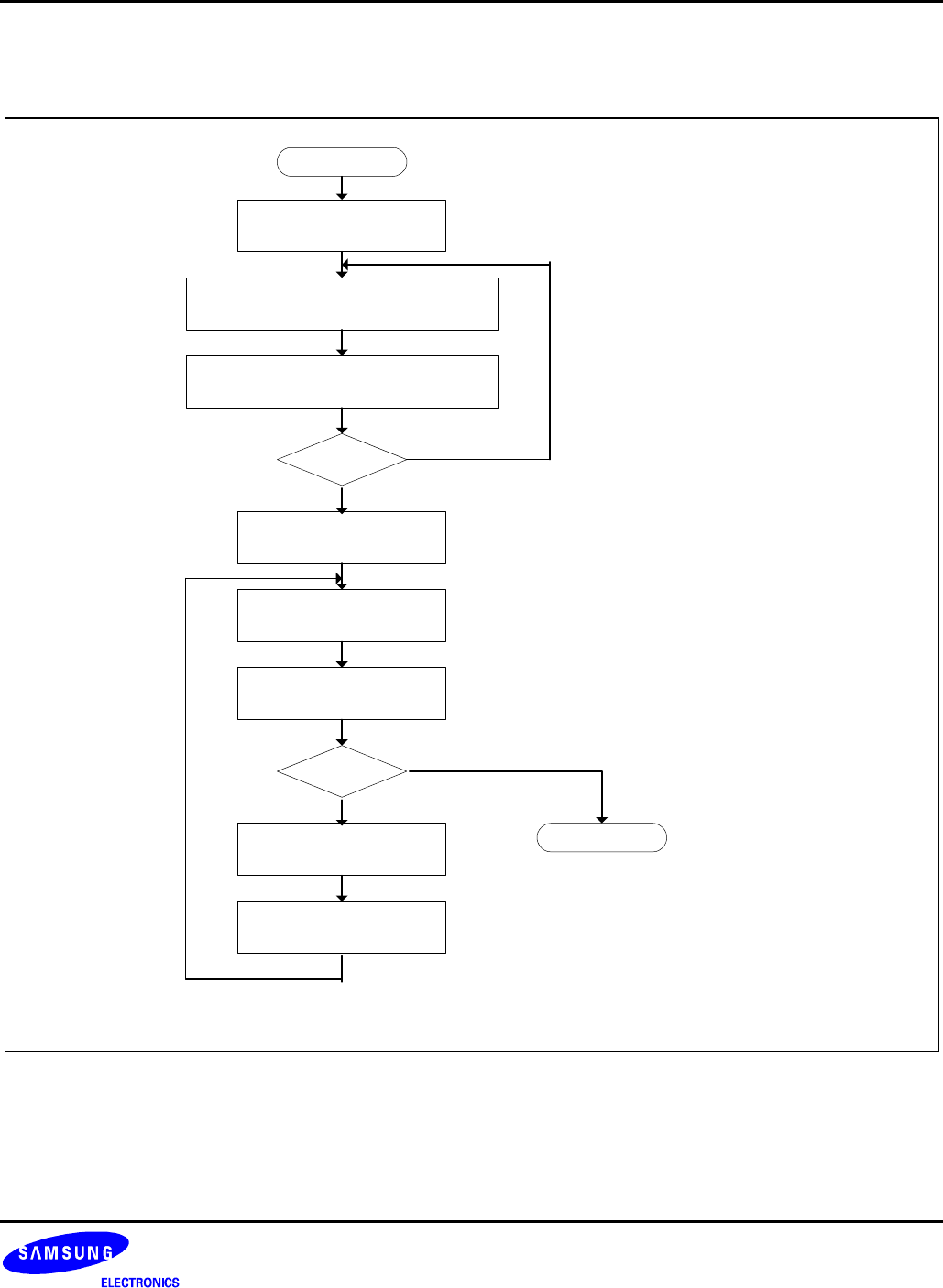

IIC detects start signal. and, IICDS

receives data.

IIC compares IICADD and IICDS (the

received slave address).

Write data to IICDS.

The IIC address match

interrupt is generated.

Clear pending bit to

resume.

The data of the IICDS is

shifted to SDA.

START

Slave Tx mode has

been configured.

END

Matched?

N

Y

Stop?

Interrupt is pending.

N

Y

Figure 20-8 Operations for Slave/Transmitter Mode