S3C2440A RISC MICROPROCESSOR CAMERA INTERFACE

23-8

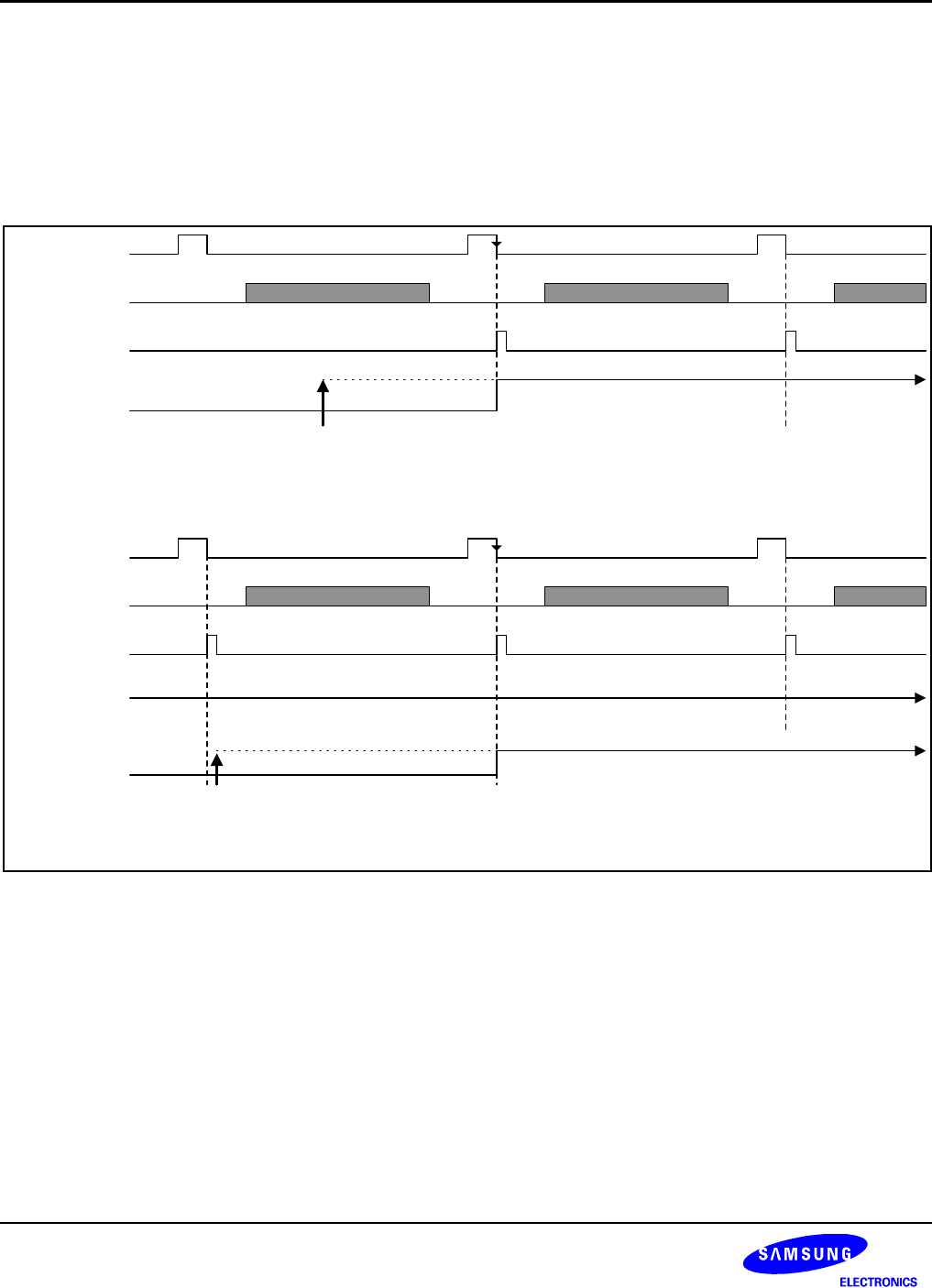

TIMING DIAGRAM FOR REGISTER SETTING

The first register setting for frame capture command can occur anywhere in the frame period. But, it is

recommended that you set it at the CAMVSYNC “L” state first and the CAMVSYNC information can be read from

the status SFR (Please see next page). All command include ImgCptEn, is valid at CAMVSYNC falling edge. But

be careful that except for first SFR setting, all command should be programmed in an ISR (Interrupt Service

Routine). Especially, capture operation should be disabled when related information for target size are changed.

jht}zuj

jht}zujjht}zuj

jht}zuj

jhtoylm

jhtoylmjhtoylm

jhtoylm

pu{lyy|w{

pu{lyy|w{pu{lyy|w{

pu{lyy|w{

zmyG

zmyGzmyG

zmyG

OpjlP

OpjlPOpjlP

OpjlP

tGG

tGGtGG

tGG

y

yy

y

pG

pGpG

pG

j

jj

j

cGmGjGzGe

cGmGjGzGecGmGjGzGe

cGmGjGzGe

jht}zuj

jht}zujjht}zuj

jht}zuj

jhtoylm

jhtoylmjhtoylm

jhtoylm

pu{lyy|w{

pu{lyy|w{pu{lyy|w{

pu{lyy|w{

uGzmyGG

uGzmyGGuGzmyGG

uGzmyGG

Gpzy

GpzyGpzy

Gpzy

pGj

pGjpGj

pGj

y

yy

y

pG

pGpG

pG

j

jj

j

cGuGGGGGe

cGuGGGGGecGuGGGGGe

cGuGGGGGe

uGj

uGjuGj

uGj

Figure 23-8 Timing Diagram for Register Setting

NOTE :

FIFO overflow of codec path will be occurred if codec path is not operating when preview path is operated. If you

want to use codec path under this case, you should stop preview path and reset CAMIF using SwRst bit of

CIGCTRL register. Then clear overflow of codec path and set special function registers that you want.