THUMB INSTRUCTION SET S3C2440A RISC MICROPROCESSOR

4-16

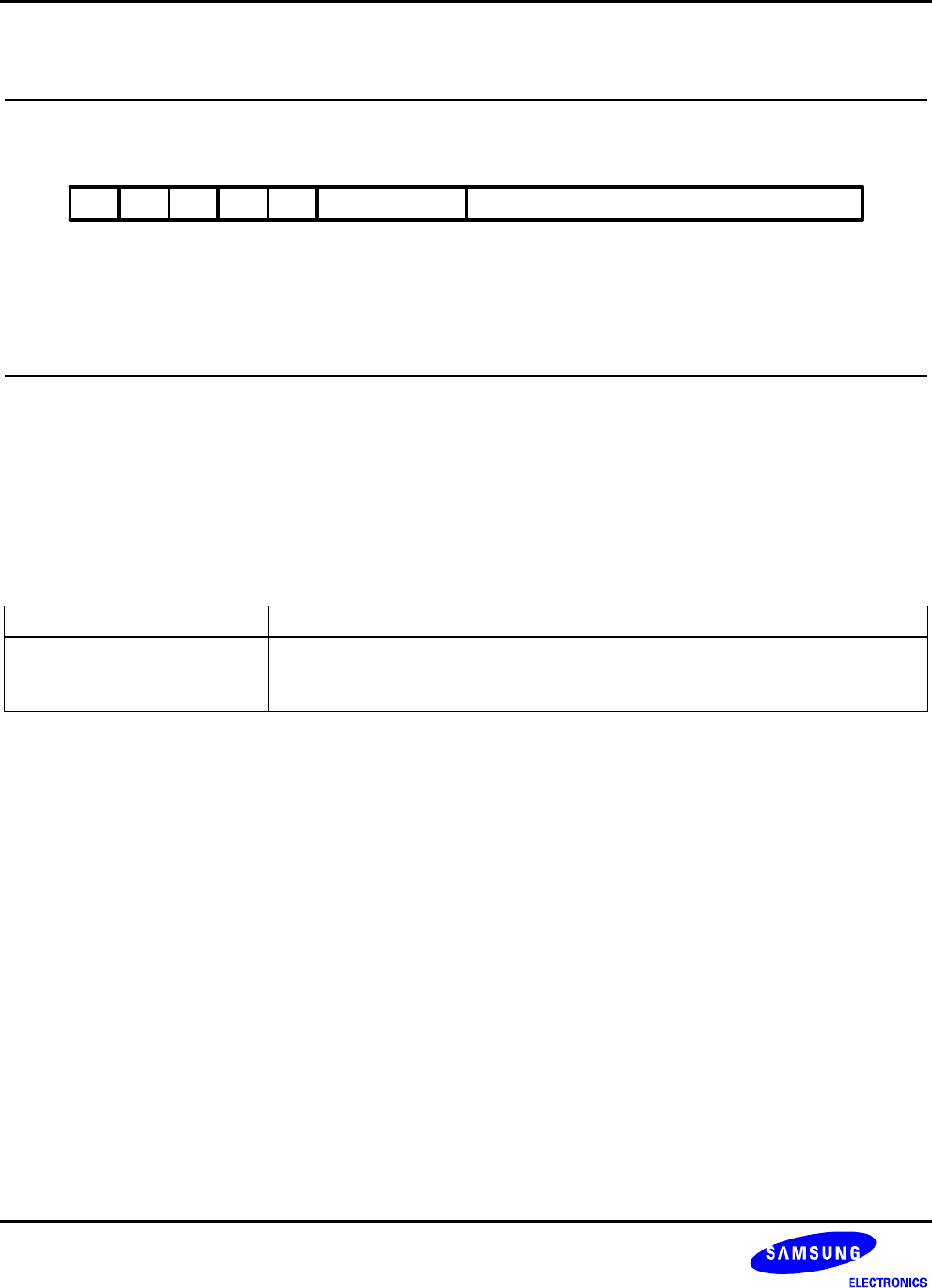

FORMAT 6: PC-RELATIVE LOAD

15 0

0

14

10

[7:0] Immediate Value

[10:8] Destination Register

Word 8

00

13 12

11

Rd0 0

87

Figure 4-7. Format 6

OPERATION

This instruction loads a word from an address specified as a 10-bit immediate offset from the PC. The THUMB

assembler syntax is shown below.

Table 4-7. Summary of PC-Relative Load Instruction

THUMB assembler ARM equivalent Description

LDR Rd, [PC, #Imm] LDR Rd, [R15, #Imm] Add unsigned offset (255 words, 1020 bytes) in

Imm to the current value of the PC. Load the

word from the resulting address into Rd.

NOTE

The value specified by #Imm is a full 10-bit address, but must always be word-aligned (ie with bits 1:0 set to 0),

since the assembler places #Imm >> 2 in field Word 8. The value of the PC will be 4 bytes greater than the address

of this instruction, but bit 1 of the PC is forced to 0 to ensure it is word aligned.