UART S3C2440A RISC MICROPROCESSOR

11-12

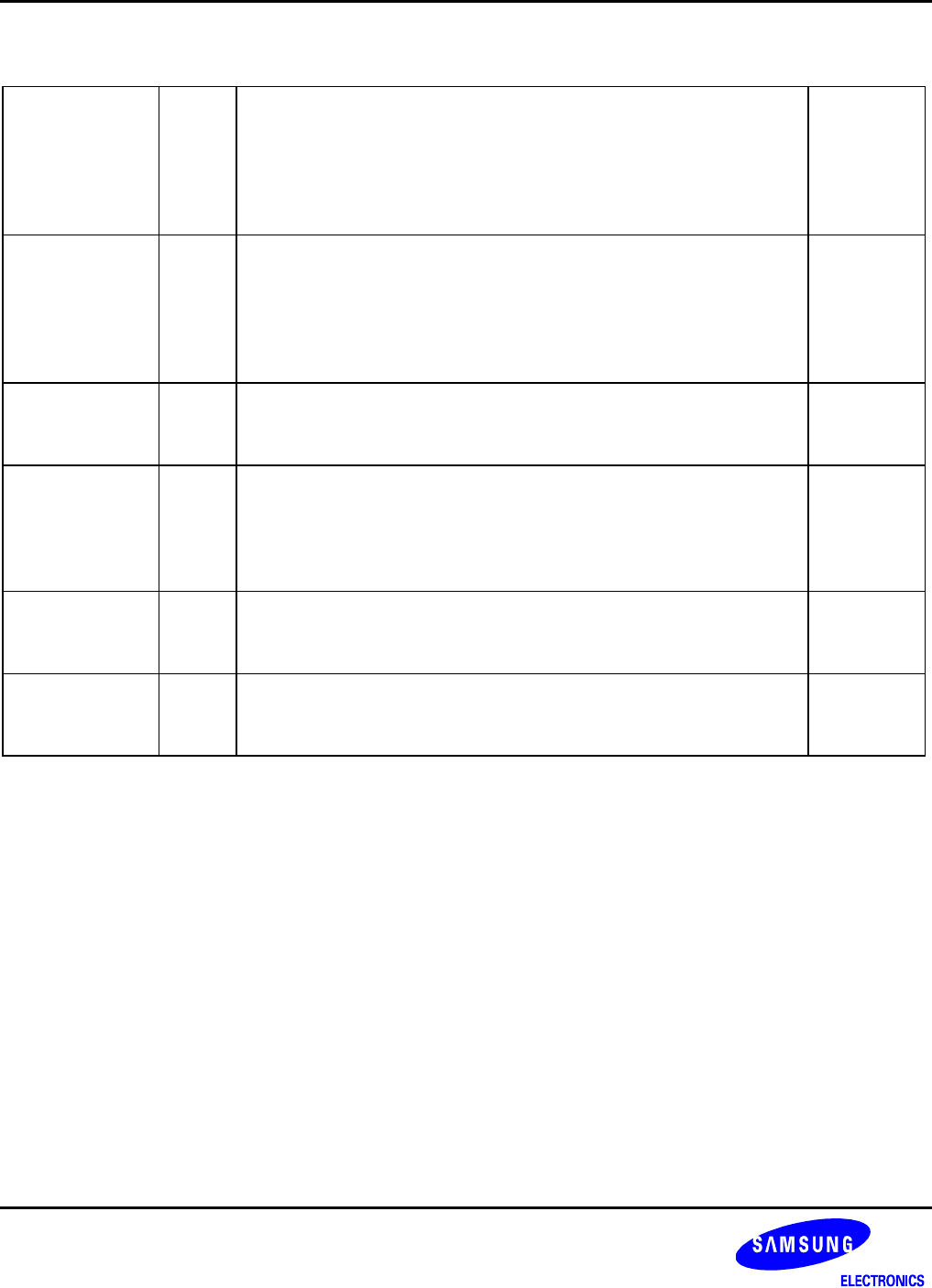

Tx Interrupt Type [9] Interrupt request type.

0 = Pulse (Interrupt is requested as soon as the Tx buffer becomes

empty in Non-FIFO mode or reaches Tx FIFO Trigger Level in FIFO

mode.)

1 = Level (Interrupt is requested while Tx buffer is empty in Non-

FIFO mode or reaches Tx FIFO Trigger Level in FIFO mode.)

0

Rx Interrupt Type [8] Interrupt request type.

0 = Pulse (Interrupt is requested the instant Rx buffer receives the

data in Non-FIFO mode or reaches Rx FIFO Trigger Level in FIFO

mode.)

1 = Level (Interrupt is requested while Rx buffer is receiving data in

Non-FIFO mode or reaches Rx FIFO Trigger Level in FIFO mode.)

0

Rx Time Out

Enable

[7] Enable/Disable Rx time out interrupt when UART FIFO is enabled.

The interrupt is a receive interrupt.

0 = Disable 1 = Enable

0

Rx Error Status

Interrupt Enable

[6] Enable the UART to generate an interrupt upon an exception, such

as a break, frame error, parity error, or overrun error during a receive

operation.

0 = Do not generate receive error status interrupt.

1 = Generate receive error status interrupt.

0

Loopback Mode [5] Setting loopback bit to 1 causes the UART to enter the loopback

mode. This mode is provided for test purposes only.

0 = Normal operation 1 = Loopback mode

0

Send Break

Signal

[4] Setting this bit causes the UART to send a break during 1 frame

time. This bit is automatically cleared after sending the break signal.

0 = Normal transmit 1 = Send break signal

0

Note

You should add following codes after selecting or deselecting the FCLK/n.

rGPHCON = rGPHCON & ~(3<<16); //GPH8(UEXTCLK) input

Delay(1); // about 100us

rGPHCON = rGPHCON & ~(3<<16) | (1<<17); //GPH8(UEXTCLK) UEXTCLK