S3C2440A RISC MICROPROCESSOR INTERRUPT CONTROLLER

14-7

INTERRUPT CONTROLLER SPECIAL REGISTERS

There are five control registers in the interrupt controller: source pending register, interrupt mode register, mask

register, priority register, and interrupt pending register.

All the interrupt requests from the interrupt sources are first registered in the source pending register. They are

divided into two groups including Fast Interrupt Request (FIQ) and Interrupt Request (IRQ), based on the interrupt

mode register. The arbitration procedure for multiple IRQs is based on the priority register.

SOURCE PENDING (SRCPND) REGISTER

The SRCPND register is composed of 32 bits each of which is related to an interrupt source. Each bit is set to 1 if

the corresponding interrupt source generates the interrupt request and waits for the interrupt to be serviced.

Accordingly, this register indicates which interrupt source is waiting for the request to be serviced. Note that each

bit of the SRCPND register is automatically set by the interrupt sources regardless of the masking bits in the

INTMASK register. In addition, the SRCPND register is not affected by the priority logic of interrupt controller.

In the interrupt service routine for a specific interrupt source, the corresponding bit of the SRCPND register has to

be cleared to get the interrupt request from the same source correctly. If you return from the ISR without clearing

the bit, the interrupt controller operates as if another interrupt request came in from the same source. In other

words, if a specific bit of the SRCPND register is set to 1, it is always considered as a valid interrupt request

waiting to be serviced.

The time to clear the corresponding bit depends on the user's requirement. If you want to receive another valid

request from the same source, you should clear the corresponding bit first, and then enable the interrupt.

You can clear a specific bit of the SRCPND register by writing a data to this register. It clears only the bit positions

of the SRCPND corresponding to those set to one in the data. The bit positions corresponding to those that are set

to 0 in the data remains as they are.

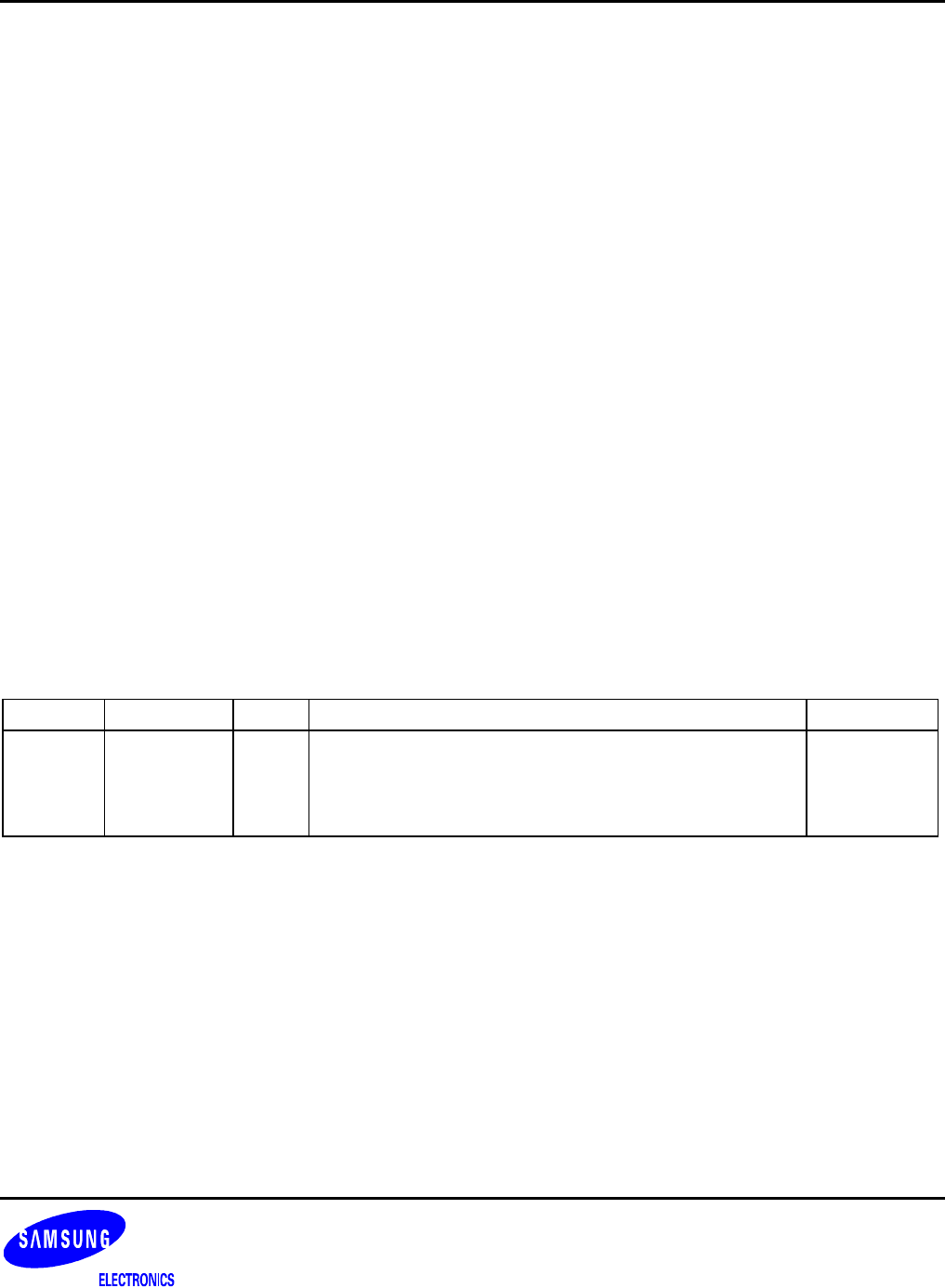

Register Address R/W Description Reset Value

SRCPND 0X4A000000 R/W Indicate the interrupt request status.

0 = The interrupt has not been requested.

1 = The interrupt source has asserted the interrupt

request.

0x00000000