NAND FLASH CONTROLLER S3C2440A RISC MICROPROCESSOR

6-8

ECC MODULE FEATURES

ECC generation is controlled by the ECC Lock (MainECCLock, SpareECCLock) bit of the Control register.

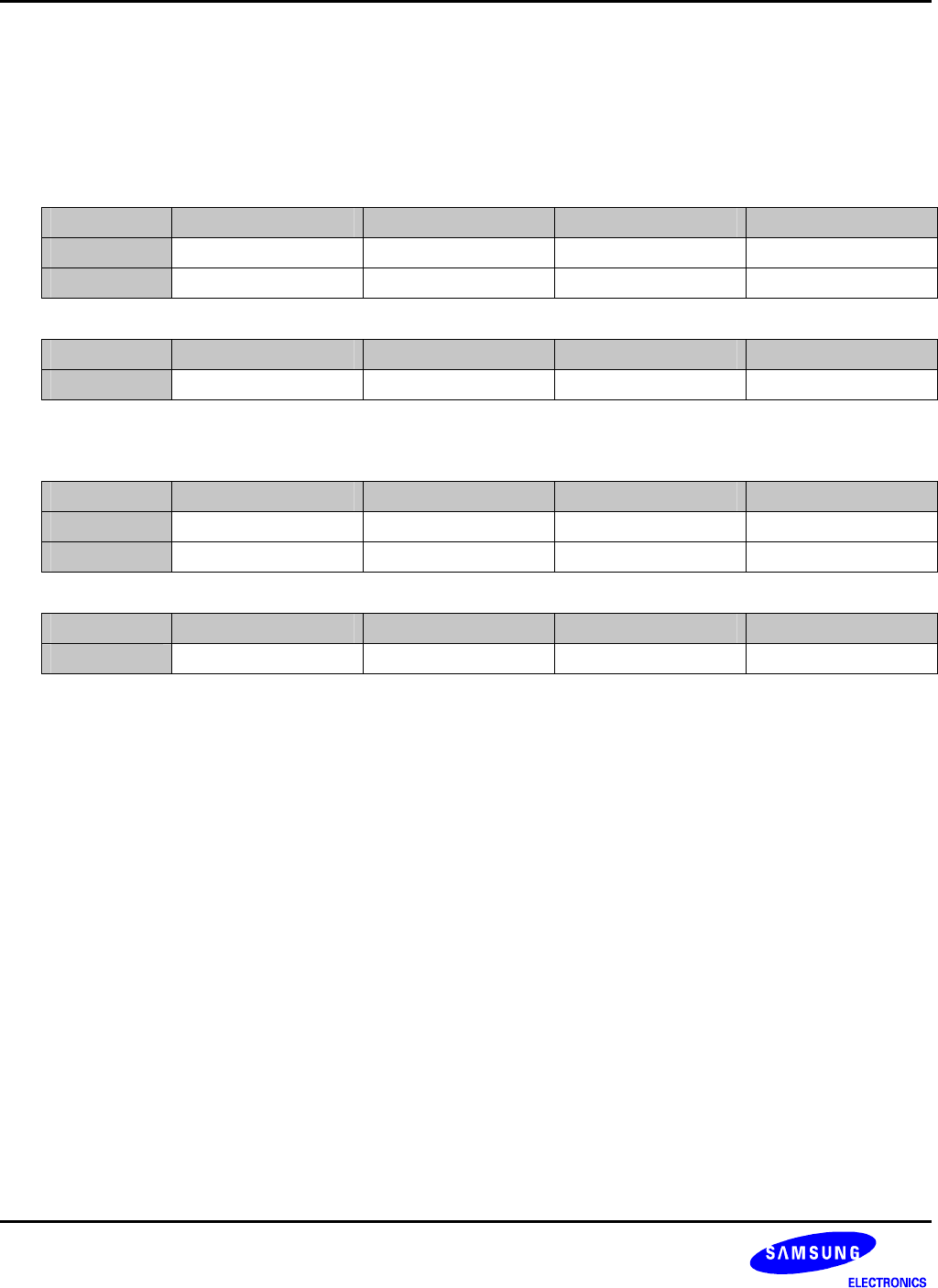

ECC Register Configuration (Little / Big Endian)

1) 16-bit NAND Flash Memory Interface

Register Bit [31:24] Bit [23:16] Bit [15:8] Bit [7:0]

NFMECCD0 2

nd

ECC for I/O[15:8] 2

nd

ECC for I/O[7:0] 1

st

ECC for I/O[15:8] 1

st

ECC for I/O[7:0]

NFMECCD1 4th ECC for I/O[15:8] 4

th

ECC for I/O[7:0] 3

rd

ECC for I/O[15:8] 3

rd

ECC for I/O[7:0]

Register Bit [31:24] Bit [23:16] Bit [15:8] Bit [7:0]

NFSECCD 2

nd

ECC for I/O[15:8] 2

nd

ECC for I/O[7:0] 1

st

ECC for I/O[15:8] 1

st

ECC for I/O[7:0]

2) 8-bit NAND Flash Memory Interface

Register Bit [31:24] Bit [23:16] Bit [15:8] Bit [7:0]

NFMECCD0 - 2

nd

ECC for I/O[7:0] - 1

st

ECC for I/O[7:0]

NFMECCD1 - 4

th

ECC for I/O[7:0] - 3

rd

ECC for I/O[7:0]

Register Bit [31:24] Bit [23:16] Bit [15:8] Bit [7:0]

NFSECCD - 2

nd

ECC for I/O[7:0] - 1

st

ECC for I/O[7:0]

ECC PROGRAMMING GUIDE

1) In software mode, ECC module generates ECC parity code for all read / write data. So you have to reset

ECC value by writing the InitECC(NFCONT[4]) bit as ‘1’ and have to clear theMainECCLock(NFCONT[5])

bit to ‘0’(Unlock) before read or write data.

MainECCLock(NFCONT[5]) and SpareECCLock(NFCONT[6]) control whether ECC Parity code is

generated or not.

2) Whenever data is read or written, the ECC module generates ECC parity code on register NFMECC0/1.

3) After you completely read or write one page (not include spare area data), Set the MainECCLock bit to

‘1’(Lock). ECC Parity code is locked and the value of the ECC status register will not be changed.

4) To generate spare area ECC parity code, Clear as ‘0’(Unlock) SpareECCLock(NFCONT[6]) bit.

5) Whenever data is read or written, the spare area ECC module generates ECC parity code on register

NFSECC.

6) After you completely read or write spare area, Set the SpareECCLock bit to ‘1’(Lock). ECC Parity code is

locked and the value of the ECC status register will not be changed.

7) Once completed you can use these values to record to the spare area or check the bit error.

(Note) NFSECCD is for ECC in the spare area (Usually, the user will write the ECC value of main data area

to Spare area, which value will be the same as NFMECC0/1) and which is generated from the main data area.