S3C2440A RISC MICROPROCESSOR ARM INSTRUCTION SET

3-19

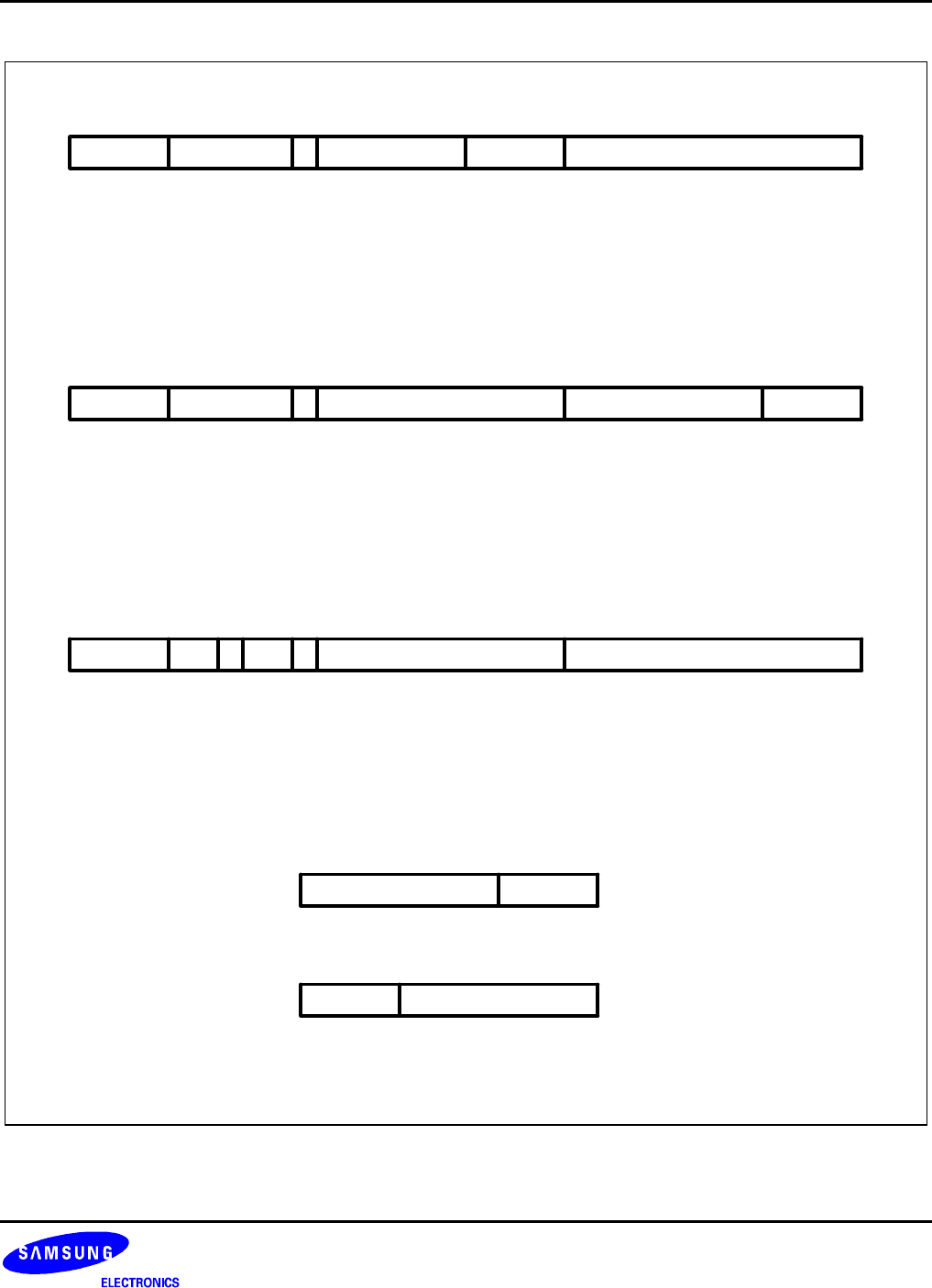

MSR (transfer register contents or immediate value to PSR flag bits only)

Cond Source operand

Pd

101001111

31 222728 11122123

I1000

26 25 24 0

Cond 00000000

00010

Pd

101001111

31 222728 11122123

Rm

MSR (transfer register contents to PSR)

43 0

Cond 000000000000

00010 Rd

Ps

001111

31 2227 1528 16 11122123

MRS (transfer PSR contents to a register)

0

[3:0] Source Register

[22] Destination PSR

0 = CPSR 1 = SPSR_<current mode>

[31:28] Condition Field

[15:12] Destination Register

[22] Source PSR

0 = CPSR 1 = SPSR_<current mode>

[31:28] Condition Field

[3:0] Source Register

[11:4] Source operand is an immediate value

[7:0] Unsigned 8 bit immediate value

[11:8] Shift applied to Imm

[22] Destination PSR

0 = CPSR 1 = SPSR_<current mode>

[25] Immediate Operand

0 = Source operand is a register

1 = SPSR_<current mode>

[11:0] Source Operand

[31:28] Condition Field

00000000 Rm

11 4 3 0

Rotate Imm

11 087

Figure 3-11. PSR Transfer