USB DEVICE S3C2440A RISC MICROPROCESSOR

13-16

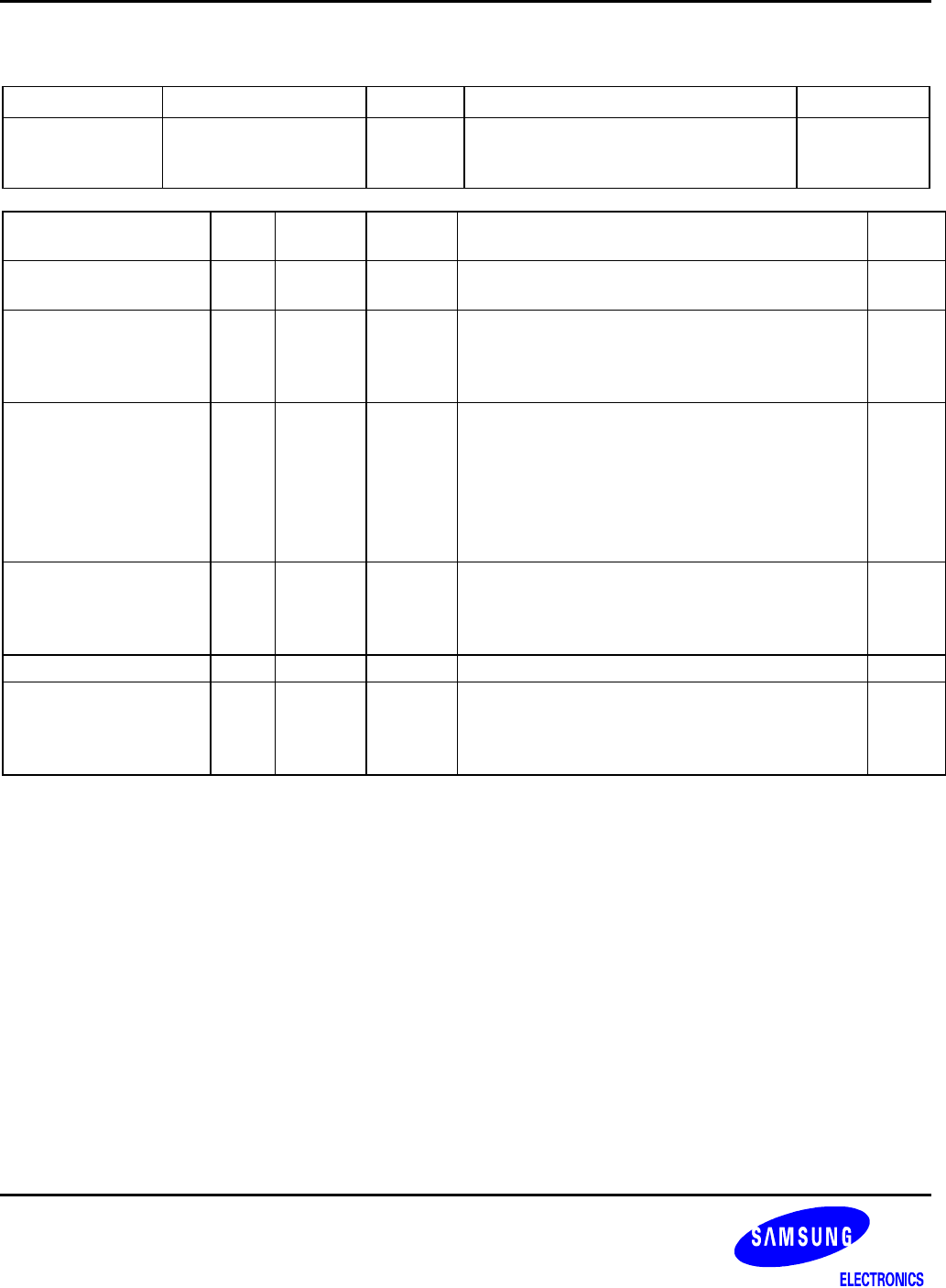

END POINT OUT CONTROL STATUS REGISTER (OUT_CSR1_REG/OUT_CSR2_REG)

Register Address R/W Description Reset Value

OUT_CSR1_REG 0x52000190(L)

0x52000193(B)

R/W

(byte)

End Point out control status register1 0x00

OUT_CSR1_REG Bit MCU USB Description Initial

State

CLR_DATA_TOGGLE [7] R/W CLEAR When the MCU writes a 1 to this bit, the data

toggle sequence bit is reset to DATA0.

0

SENT_STALL [6] CLEAR

/R

SET Set by the USB when an OUT token is ended

with a STALL handshake. The USB issues a

stall handshake to the host if it sends more than

MAXP data for the OUT TOKEN.

0

SEND_STALL [5] R/W R 0: The MCU clears this bit to end the STALL

condition handshake, IN PKT RDY is

cleared.

1: The MCU issues a STALL handshake to the

USB. The MCU clears this bit to end the

STALL condition handshake, IN PKT RDY

is cleared.

0

FIFO_FLUSH [4] R/W CLEAR The MCU writes a 1 to flush the FIFO.

This bit can be set only when OUT_PKT_RDY

(D0) is set. The packet due to be unloaded by

the MCU will be flushed.

0

Reserved [3:1] - -

-

0

OUT_PKT_RDY [0] R/

CLEAR

SET Set by the USB after it has loaded a packet of

data into the FIFO. Once the MCU reads the

packet from FIFO, this bit should be cleared by

MCU (write a "0").

0