S3C2440A RISC MICROPROCESSOR AC97 CONTROLLER

24-7

Waking up the AC-link - Wake Up Triggered by the AC97 Controller

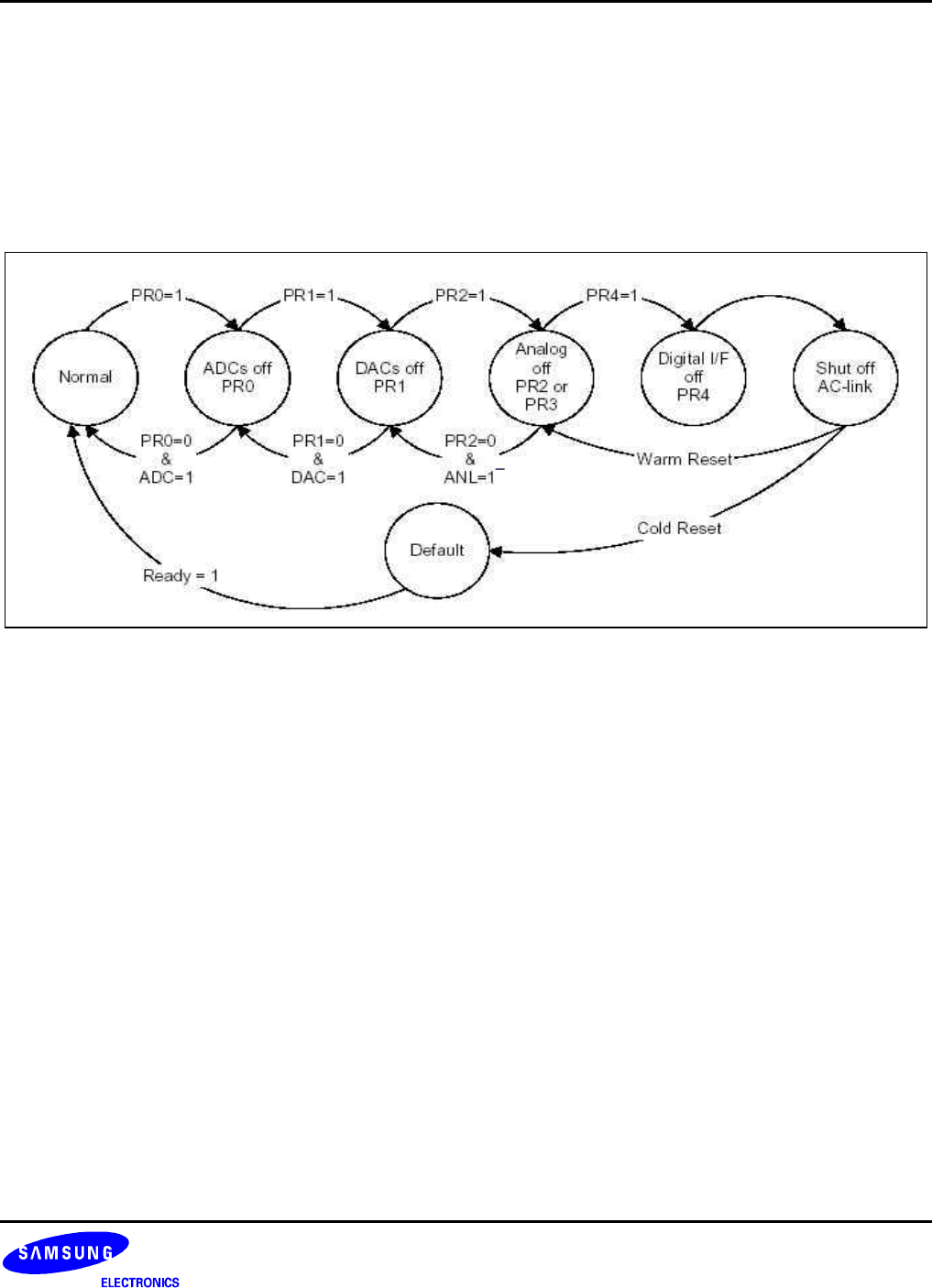

AC-link protocol is provided for a cold AC97 reset and a warm AC97 reset. The current power-down state

ultimately dictates which AC97 reset is used. Registers must stay in the same state during all power-down modes

unless a cold AC97 reset is performed. In a cold AC97 reset, the AC97 registers are initialized to their default

values. After a power down, the AC-link must wait for a minimum of four audio frame time after the frame in which

the power down occurred before it can be reactivated by reasserting the SYNC signal. When AC-link powers up, it

indicates readiness through the Codec ready bit (input slot 0, bit 15).

Figure 24-8 AC97 Power down/Power up Flow

Cold AC97 Reset

A cold reset is generated when an nRESET pin is asserted through the AC_GLBCTRL. Asserting and de-asserting

nRESET activates the BITCLK and SDATA_OUT. All the AC97 control registers are initialized to their default

power on reset values. nRESET is an asynchronous AC97 input.

Warm AC97 Reset

A warm AC97 reset reactivates the AC-link without altering the current AC97 register values. A warm reset is

generated when BITCLK is absent and SYNC is driven high. In normal audio frames, SYNC is a synchronous

AC97 input. When BITCLK is absent, SYNC is treated as an asynchronous input used to generate a warm reset to

AC97.The AC97 Controller must not activate BITCLK until it samples the SYNC to low again. This prevents a new

audio frame from being falsely detected.