S3C2440A RISC MICROPROCESSOR THUMB INSTRUCTION SET

4-19

OPERATION

These instructions transfer byte or word values between registers and memory. Memory addresses are pre-

indexed using an offset register in the range 0-7. The THUMB assembler syntax is shown in Table 4-8.

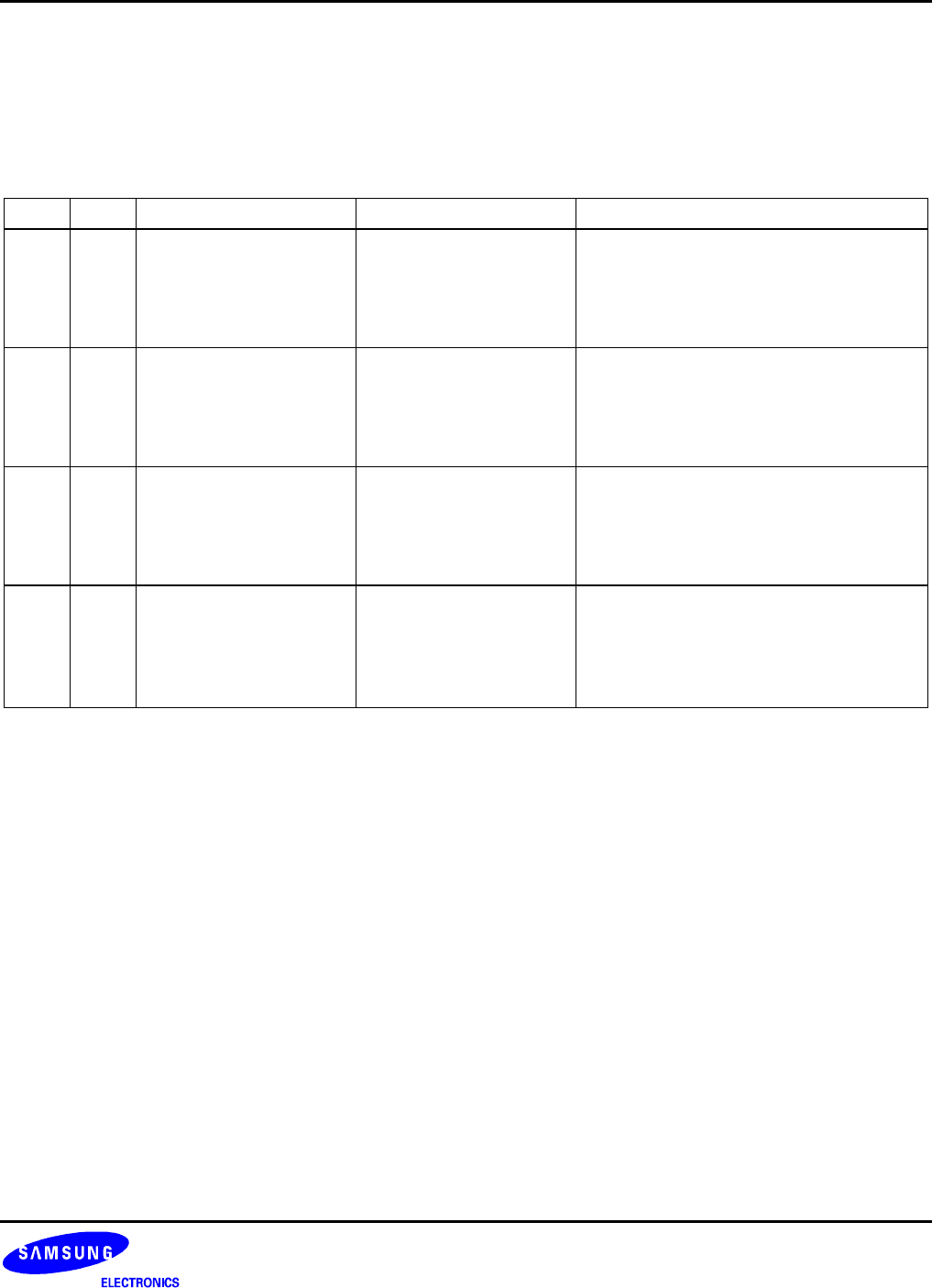

Table 4-8. Summary of Format 7 Instructions

L B THUMB assembler ARM equivalent Description

0 0 STR Rd, [Rb, Ro] STR Rd, [Rb, Ro] Pre-indexed word store:

Calculate the target address by adding

together the value in Rb and the value in

Ro. Store the contents of Rd at the

address.

0 1 STRB Rd, [Rb, Ro] STRB Rd, [Rb, Ro] Pre-indexed byte store:

Calculate the target address by adding

together the value in Rb and the value in

Ro. Store the byte value in Rd at the

resulting address.

1 0 LDR Rd, [Rb, Ro] LDR Rd, [Rb, Ro] Pre-indexed word load:

Calculate the source address by adding

together the value in Rb and the value in

Ro. Load the contents of the address into

Rd.

1 1

LDRB Rd, [Rb, Ro] LDRB Rd, [Rb, Ro] Pre-indexed byte load:

Calculate the source address by adding

together the value in Rb and the value in

Ro. Load the byte value at the resulting

address.

INSTRUCTION CYCLE TIMES

All instructions in this format have an equivalent ARM instruction as shown in Table 4-8. The instruction cycle

times for the THUMB instruction are identical to that of the equivalent ARM instruction.

EXAMPLES

STR R3, [R2,R6] ; Store word in R3 at the address

formed by adding R6 to R2.

LDRB R2, [R0,R7] ; Load into R2 the byte found at

the address formed by adding R7 to R0.