S3C2440A RISC MICROPROCESSOR AC97 CONTROLLER

24-5

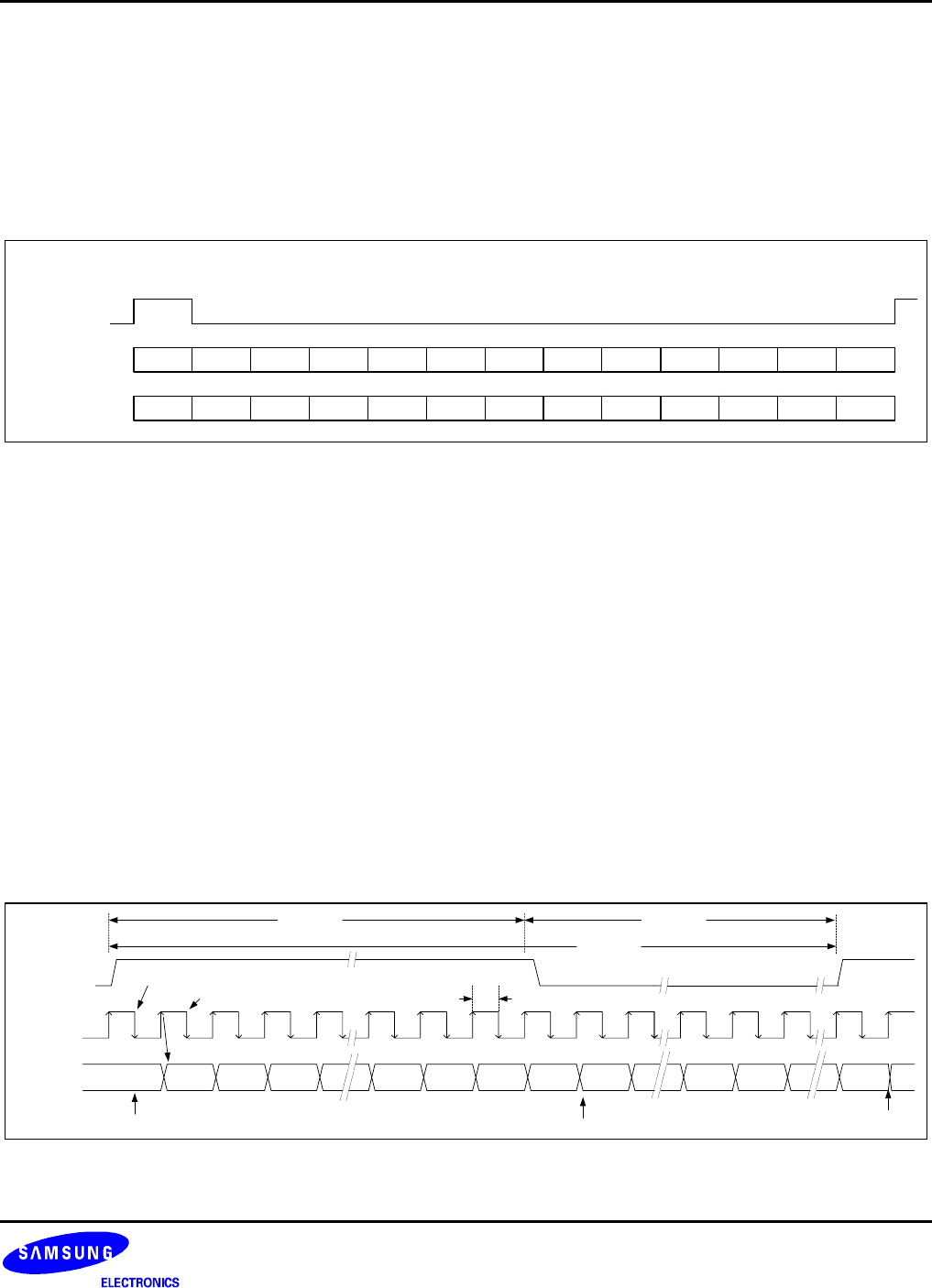

AC-LINK DIGITAL INTERFACE PROTOCOL

Each AC97 Codec incorporates a five-pin digital serial interface that links it to the S3C2440A AC97 Controller. The

AC-link is a full-duplex, fixed-clock, PCM digital stream. It employs a time division multiplexing (TDM) scheme to

handle control register access and multiple input and output audio streams. The AC-link architecture divides each

audio frame into 12 outgoing and 12 incoming data streams. Each stream has a 20-bit sample resolution and

requires a DAC and an analog-to-digital converter (ADC) with a minimum of 16-bit resolution.

SYNC

SDATA_OUT

SDATA_IN

Slot #

TAG

CMD

ADDR

CMD

DATA

PCM PCM

RSRVD

TAG

STATUS

ADDR

STATUS

DATA

PCM

LEFT

PCM

RIGHT

0123456789101112

RSRVDRSRVDRSRVDRSRVDRSRVDRSRVDRSRVD

RSRVD RSRVD RSRVD RSRVD RSRVD RSRVD RSRVD

PCM

MIC

LEFT RIGHT

Figure 24-4 Bi-directional AC-link Frame with Slot Assignments

Figure 24-4 shows the slot definitions supported by the S3C2440A AC97 Controller. The S3C2440A AC97

Controller provides synchronization for all data transaction on the AC-link.

A data transaction is made up of 256-bits of information broken up into groups of 13 time slots and is called a

frame. Time slot 0 is called as Tag Phase and it is 16-bits long. The remaining 12 time slots are called as Data

Phase. The Tag Phase contains a bit that identifies a valid frame and 12-bits that identify the time slots in the Data

Phase that contain a valid data. Each time slot in the Data Phase is 20-bits long. A frame begins when the SYNC

goes high. The amount of time the SYNC is high corresponds to the Tag Phase.

AC97 frames occur at fixed 48 KHz intervals and are synchronous to the 12.288 MHz bit rate clock, BITCLK. The

controller and the CODEC use the SYNC and BITCLK to determine when to send the transmit data and when to

sample the received data. A transmitter transitions the serial data stream on each rising edge of BITCLK and a

receiver samples the serial data stream on falling edges of BITCLK. The transmitter must tag the valid slots in its

serial data stream. The valid slots are tagged in slot 0. Serial data on the AC-link is from MSB to LSB. The Tag

Phase’s first bit is bit 15 and the first bit of each slot in the Data Phase is bit 19. The last bit in any slot is bit 0.

AC-LINK OUTPUT FRAME (SDATA_OUT)

SDATA_OUT

BIT_CLK

SYNC

AC '97 samples SYNC assertion here

AC '97 Controller samples first SDATA_OUT bit of frame here

END of previous Audio Frame

Valid

Frame

Slot(1) Slot(2)

Slot(12) "0" ID1 ID0 19 0

Tag Phase Data Phase

19 0

START of Data phase

Slot# 1

END of Data Frame

Slot# 12

48KHz

12.288MHz

Figure 24-5 AC-link Output Frame