S3C2440A RISC MICROPROCESSOR THUMB INSTRUCTION SET

4-37

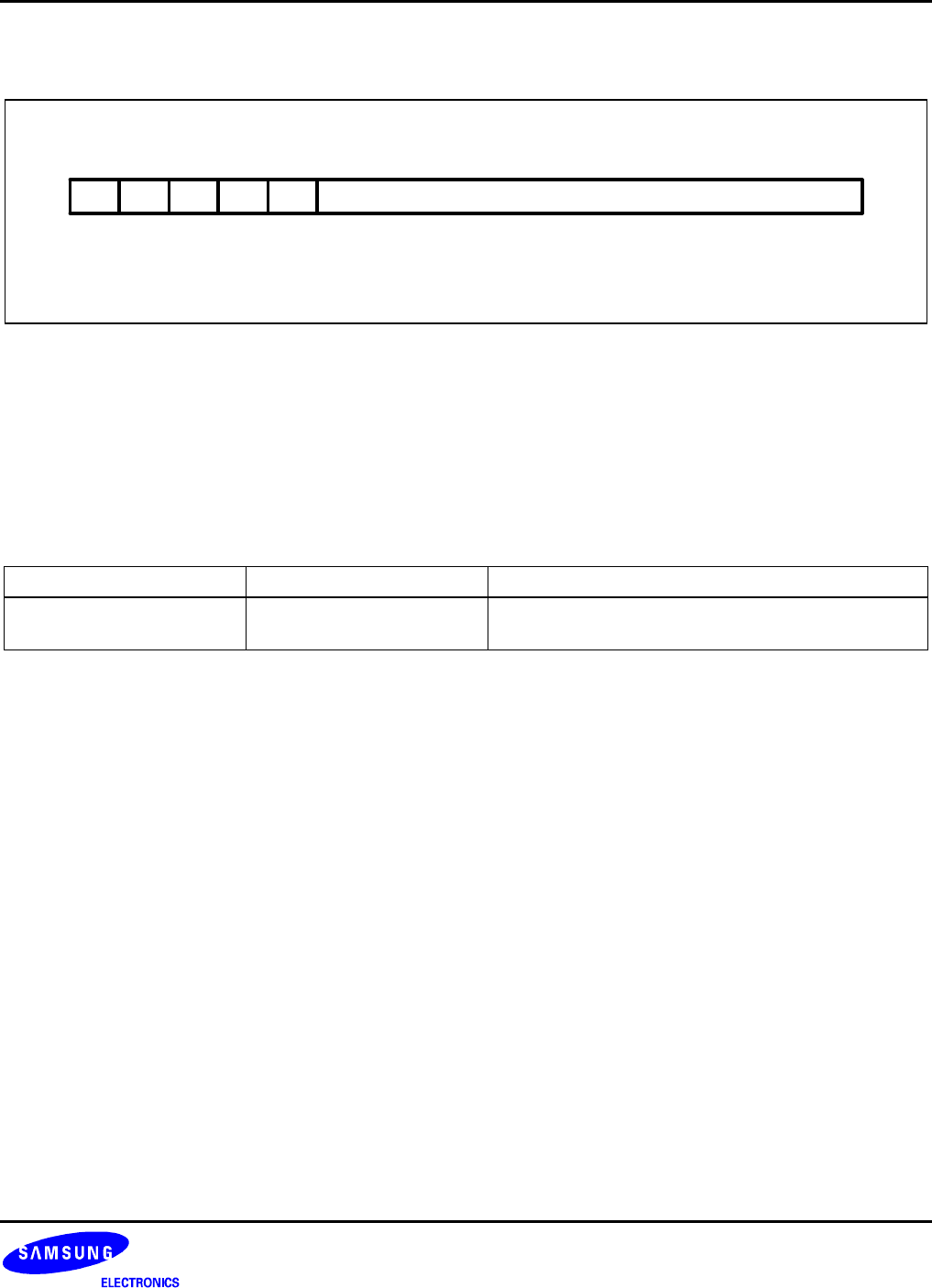

FORMAT 18: UNCONDITIONAL BRANCH

[10:0] Immediate Value

15 0

1

14

11

13 12

11

Offset11

0

10

0

Figure 4-19. Format 18

OPERATION

This instruction performs a PC-relative Branch. The THUMB assembler syntax is shown below. The branch offset

must take account of the prefetch operation, which causes the PC to be 1 word (4 bytes) ahead of the current

instruction.

Table 4-19. Summary of Branch Instruction

THUMB assembler ARM equivalent Description

B label BAL label (halfword offset) Branch PC relative +/- Offset11 << 1, where label is

PC +/- 2048 bytes.

NOTE

The address specified by label is a full 12-bit two's complement address,

but must always be halfword aligned (ie bit 0 set to 0), since the assembler places label >> 1 in the Offset11 field.

EXAMPLES

here B here ; Branch onto itself. Assembles to 0xE7FE.

(Note effect of PC offset).

B jimmy ; Branch to 'jimmy'.

• Note that the THUMB opcode will contain the number of

•

• ; halfwords to offset.

jimmy

• Must be halfword aligned.