S3C2440A RISC MICROPROCESSOR ARM INSTRUCTION SET

3-49

SOFTWARE INTERRUPT (SWI)

The instruction is only executed if the condition is true. The various conditions are defined in Table 3-2. The

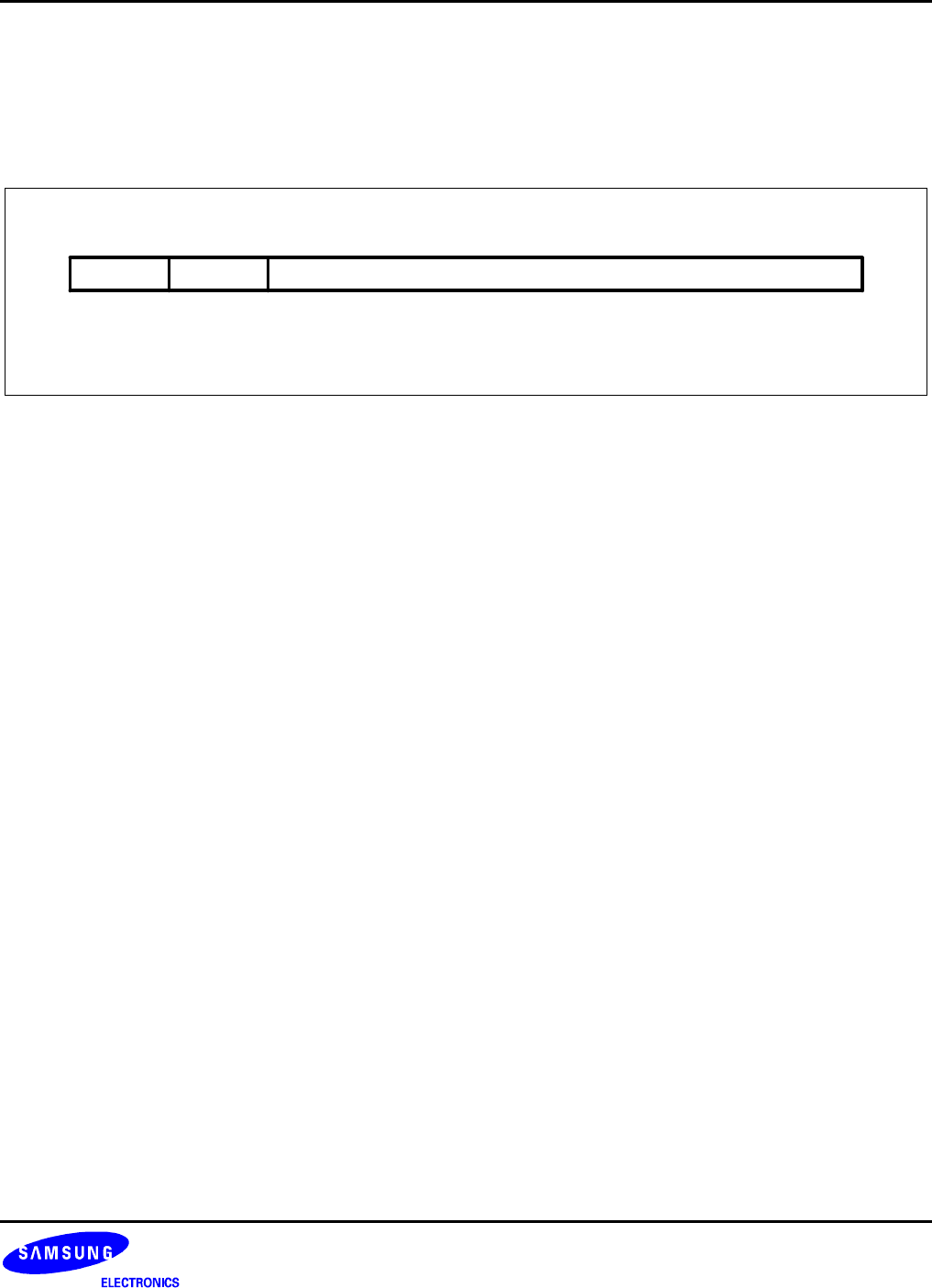

instruction encoding is shown in Figure 3-24, below.

31 2427

1111

Cond Comment Field (Ignored by Processor)

28 23

[31:28] Condition Field

0

Figure 3-24. Software Interrupt Instruction

The software interrupt instruction is used to enter Supervisor mode in a controlled manner. The instruction causes

the software interrupt trap to be taken, which effects the mode change. The PC is then forced to a fixed value

(0x08) and the CPSR is saved in SPSR_svc. If the SWI vector address is suitably protected (by external memory

management hardware) from modification by the user, a fully protected operating system may be constructed.

RETURN FROM THE SUPERVISOR

The PC is saved in R14_svc upon entering the software interrupt trap, with the PC adjusted to point to the word

after the SWI instruction. MOVS PC,R14_svc will return to the calling program and restore the CPSR.

Note that the link mechanism is not re-entrant, so if the supervisor code wishes to use software interrupts within

itself it must first save a copy of the return address and SPSR.

COMMENT FIELD

The bottom 24 bits of the instruction are ignored by the processor, and may be used to communicate information

to the supervisor code. For instance, the supervisor may look at this field and use it to index into an array of entry

points for routines which perform the various supervisor functions.

INSTRUCTION CYCLE TIMES

Software interrupt instructions take 2S + 1N incremental cycles to execute, where S and N are defined as

sequential (S-cycle) and non-sequential (N-cycle).