S3C2440A RISC MICROPROCESSOR THUMB INSTRUCTION SET

4-11

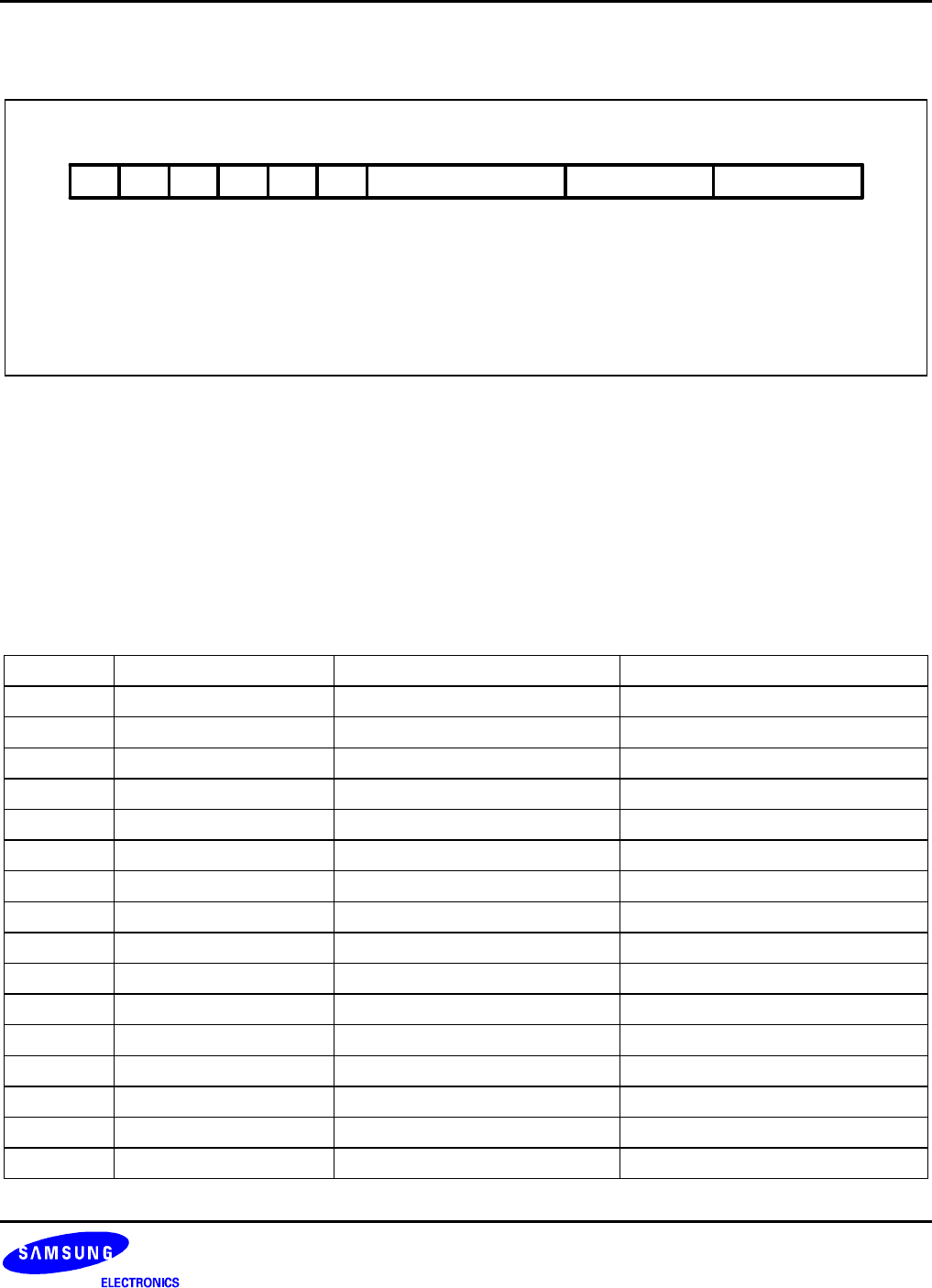

FORMAT 4: ALU OPERATIONS

15 0

0

14

10

[2:0] Source/Destination Register

[5:3] Source Register 2

[9:6] Opcode

56

3

Rd

00

13 12

11

Op

Rs

0 00

9 2

Figure 4-5. Format 4

OPERATION

The following instructions perform ALU operations on a Lo register pair.

NOTE

All instructions in this group set the CPSR condition codes.

Table 4-5. Summary of Format 4 Instructions

OP THUMB Assembler ARM Equipment Description

0000 AND Rd, Rs ANDS Rd, Rd, Rs Rd:= Rd AND Rs

0001 EOR Rd, Rs EORS Rd, Rd, Rs Rd:= Rd EOR Rs

0010 LSL Rd, Rs MOVS Rd, Rd, LSL Rs Rd := Rd << Rs

0011 LSR Rd, Rs MOVS Rd, Rd, LSR Rs Rd := Rd >> Rs

0100 ASR Rd, Rs MOVS Rd, Rd, ASR Rs Rd := Rd ASR Rs

0101 ADC Rd, Rs ADCS Rd, Rd, Rs Rd := Rd + Rs + C-bit

0110 SBC Rd, Rs SBCS Rd, Rd, Rs Rd := Rd - Rs - NOT C-bit

0111 ROR Rd, Rs MOVS Rd, Rd, ROR Rs Rd := Rd ROR Rs

1000 TST Rd, Rs TST Rd, Rs Set condition codes on Rd AND Rs

1001 NEG Rd, Rs RSBS Rd, Rs, #0 Rd = - Rs

1010 CMP Rd, Rs CMP Rd, Rs Set condition codes on Rd - Rs

1011 CMN Rd, Rs CMN Rd, Rs Set condition codes on Rd + Rs

1100 ORR Rd, Rs ORRS Rd, Rd, Rs Rd := Rd OR Rs

1101 MUL Rd, Rs MULS Rd, Rs, Rd Rd := Rs * Rd

1110 BIC Rd, Rs BICS Rd, Rd, Rs Rd := Rd AND NOT Rs

1111 MVN Rd, Rs MVNS Rd, Rs Rd := NOT Rs