DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

108 of 344

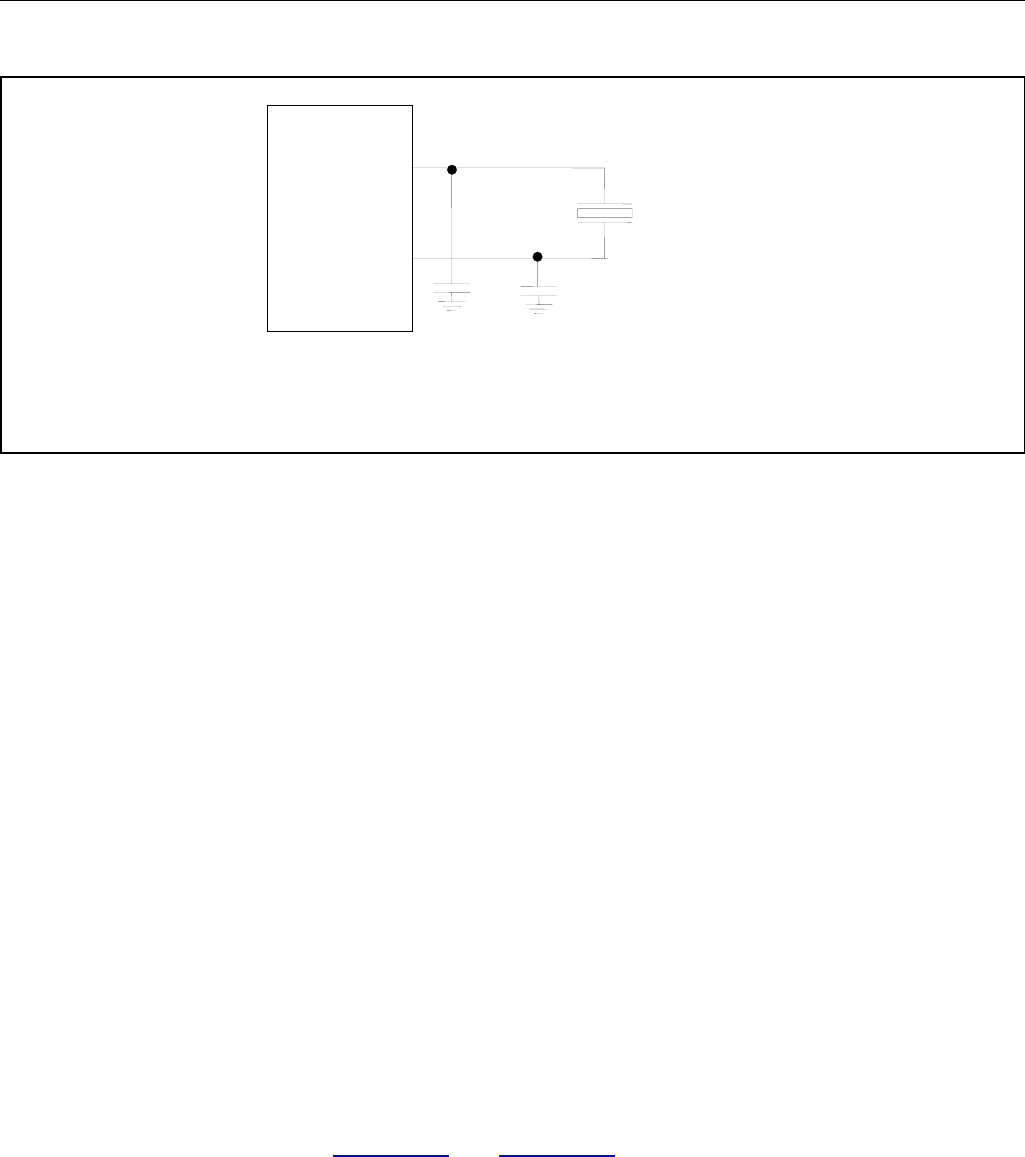

Figure 10-14. Optional Crystal Connections

XTALD

C1

C2

1.544MHz/2.048MHz

MCLK

NOTE: C1 AND C2 SHOULD BE 5pF LOWER THAN TWO TIMES THE NOMINAL LOADING CAPACITANCE

OF THE CRYSTAL TO ADJUST FOR THE INPUT CAPACITANCE OF THE DEVICE.

10.25 T1/E1/J1 TRANSCEIVER BERT FUNCTION

The BERT block can generate and detect pseudorandom and repeating bit patterns. It is used to test and stress

data communication links, and it is capable of generating and detecting the following patterns:

The pseudorandom patterns 2E7, 2E11, 2E15, and QRSS

A repetitive pattern from 1 to 32 bits in length

Alternating (16-bit) words that flip every 1 to 256 words

Daly pattern

The BERT receiver has a 32-bit bit counter and a 24-bit error counter. The BERT receiver reports three events: a

change in receive synchronizer status, a bit error being detected, and if either the bit counter or the error counter

overflows. Each of these events can be masked within the BERT function through the BERT control register 1

(TR.BC1). If the software detects that the BERT has reported an event, then the software must read the BERT

information register (BIR) to determine which event(s) has occurred. To activate the BERT block, the host must

configure the BERT mux through the TR.BIC register.

10.25.1 BERT Status

TR.SR9 contains the status information on the BERT function. The host can be alerted through this register when

there is a BERT change-of-state. A major change-of-state is defined as either a change in the receive

synchronization (i.e., the BERT has gone into or out of receive synchronization), a bit error has been detected, or

an overflow has occurred in either the bit counter or the error counter. The host must read status register 9

(TR.SR9) to determine the change-of-state.

10.25.2 BERT Mapping

The BERT function can be assigned to the network direction or backplane direction through the direction control bit

in the BIC register (TR.BIC.1). See

Figure 10-15 and Figure 10-16. The BERT also can be assigned on a per-

channel basis. The BERT transmit control selector (BTCS) and BERT receive control selector (BRCS) bits of the

per-channel pointer register (TR.PCPR) are used to map the BERT function into time slots of the transmit and

receive data streams. In T1 mode, the user can enable mapping into the F-bit position for the transmit and receive

directions through the RFUS and TFUS bits in the BERT interface control (TR.BIC) register.