DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

218 of 344

Register Name:

TR.IMR2

Register Description:

Interrupt Mask Register 2

Register Address:

19h

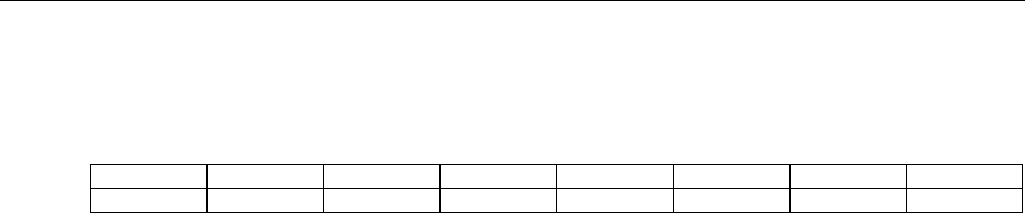

Bit # 7 6 5 4 3 2 1 0

Name RYELC RUA1C FRCLC RLOSC RYEL RUA1 FRCL RLOS

Default 0 0 0 0 0 0 0 0

Bit 7: Receive Yellow Alarm Clear Event (RYELC)

0 = interrupt masked

1 = interrupt enabled

Bit 6: Receive Unframed All-Ones Condition Clear Event (RUA1C)

0 = interrupt masked

1 = interrupt enabled

Bit 5: Framer Receive Carrier Loss Condition Clear (FRCLC)

0 = interrupt masked

1 = interrupt enabled

Bit 4: Receive Loss-of-Sync Clear Event (RLOSC)

0 = interrupt masked

1 = interrupt enabled

Bit 3: Receive Yellow Alarm Condition (RYEL)

0 = interrupt masked

1 = interrupt enabled—interrupts on rising edge only

Bit 2: Receive Unframed All-Ones (Blue Alarm) Condition (RUA1)

0 = interrupt masked

1 = interrupt enabled—interrupts on rising edge only

Bit 1: Framer Receive Carrier Loss Condition (FRCL)

0 = interrupt masked

1 = interrupt enabled—interrupts on rising edge only

Bit 0: Receive Loss-of-Sync Condition (RLOS)

0 = interrupt masked

1 = interrupt enabled—interrupts on rising edge only