DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

307 of 344

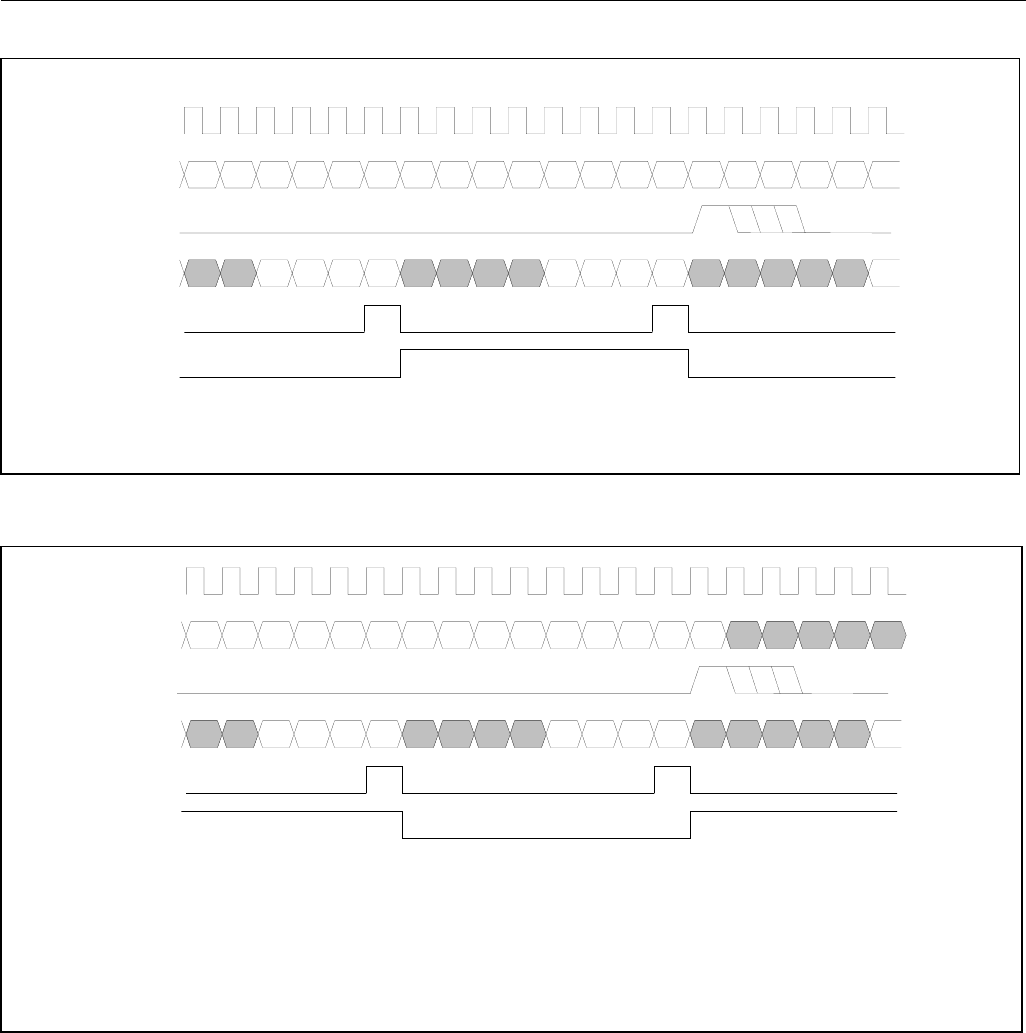

Figure 12-18. Transmit-Side 1.544MHz Boundary Timing (Elastic Store Enabled)

LSB F MSBLSB MSB

CHANNEL 1CHANNEL 24

ABC/AD/B ABC/AD/B

TSYSCLK

TSERI

TSSYNC

TSIG

TCHCLK

TCHBLK

CHANNEL 23

A

CHANNEL 23 CHANNEL 24 CHANNEL 1

1

NOTE 1: TCHBLK IS PROGRAMMED TO BLOCK CHANNEL 24 (IF THE TPCSI BIT IS SET, THEN THE SIGNALING DATA AT TSIG IS

IGNORED DURING CHANNEL 24).

Figure 12-19. Transmit-Side 2.048MHz Boundary Timing (Elastic Store Enabled)

LSB

F

LSB MSB

CHANNEL 1CHANNEL 32

ABC/AD/B ABC/AD/B

TSYSCLK

TSERI

TSSYNC

TSIG

TCHCLK

TCHBLK

CHANNEL 31

A

CHANNEL 31 CHANNEL 32 CHANNEL 1

1

4

2,3

NOTE 1: TSERI DATA IN CHANNELS 1, 5, 9, 13, 17, 21, 25, AND 29 IS IGNORED.

NOTE 2: TCHBLK IS PROGRAMMED TO BLOCK CHANNEL 31 (IF THE TPCSI BIT IS SET, THEN THE SIGNALING DATA AT TSIG WILL BE

IGNORED).

NOTE 3: TCHBLK IS FORCED TO 1 IN THE SAME CHANNELS AS TSERI IS IGNORED (SEE NOTE 1).

NOTE 4: THE F-BIT POSITION FOR THE T1 FRAME IS SAMPLED AND PASSED THROUGH THE TRANSMIT-SIDE ELASTIC STORE INTO THE MSB

BIT POSITION OF CHANNEL 1. (NORMALLY, THE TRANSMIT-SIDE FORMATTER OVERWRITES THE F-BIT POSITION UNLESS THE FORMATTER

IS PROGRAMMED TO PASS THROUGH THE F-BIT POSITION.)