DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

115 of 344

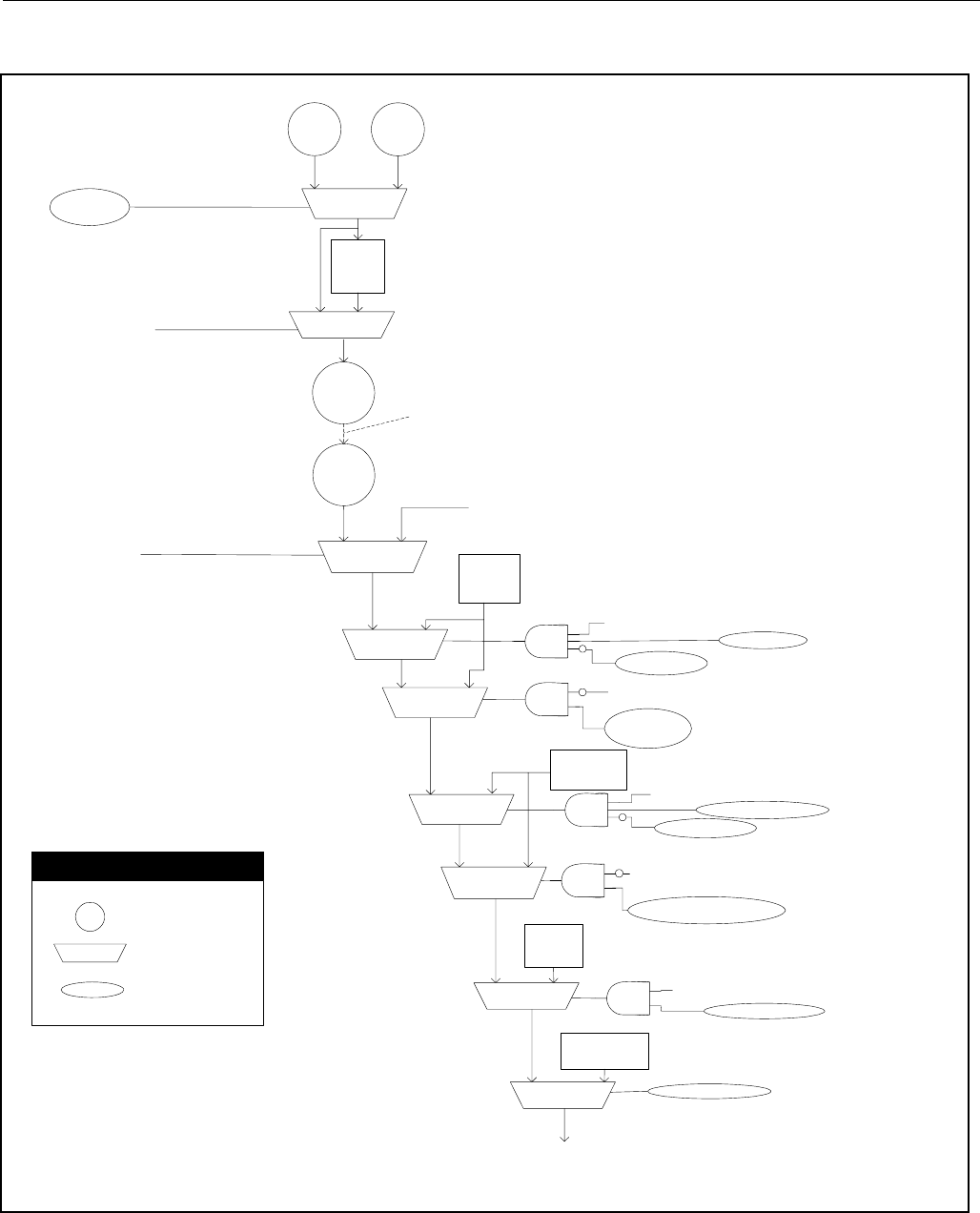

Figure 10-18. E1 Transmit Flow Diagram

TSER

TSIG

HSIE1-4

through

PCPR

TX

ESTORE

ESCR.4 TESE

TESO

TDATA

Off-Chip

Connection

RDATA

From

E1_rcv_logic

LBCR1.1 PLB

HDLC

Engine

#1

THMS1 H1TC.4

H1TCS1-4

H1TTSBS

T1SaBE4-

T1SaBE8

THMS1 H1TC.4

H1TTSBS.4 - H1TTSBS.0

HDLC

Engine #2

THMS2 H2TC.4

H2TCS1-4

H2TTSBS

T2SaBE4-T2SaBE8

THMS2 H2TC.4

H2TTSBS.4 - H2TTSBS.0

BTCS1-4

BERTEN (BIC.0)

from PCPR

BERT

Engine

To Per-Channel Mux

E1 TRANSMIT

FLOW

DIAGRAM

KEY

- PIN

- SELECTOR

- REGISTER

Hardware

Signaling

Estore Mux

Payload

Loopback Mux

HDLC DS0

Mux #1

HDLC Sa-bit

Mux #1

HDLC DS0

Mux #2

BERT Mux

HDLC Sa-bit

Mux #2

Idle Code MUX

Idle Code

Array

TCICE1-4