DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

266 of 344

Register Name:

TR.H1FC, TR.H2FC

Register Description:

HDLC # 1 FIFO Control

HDLC # 2 FIFO Control

Register Address:

91h, A1h

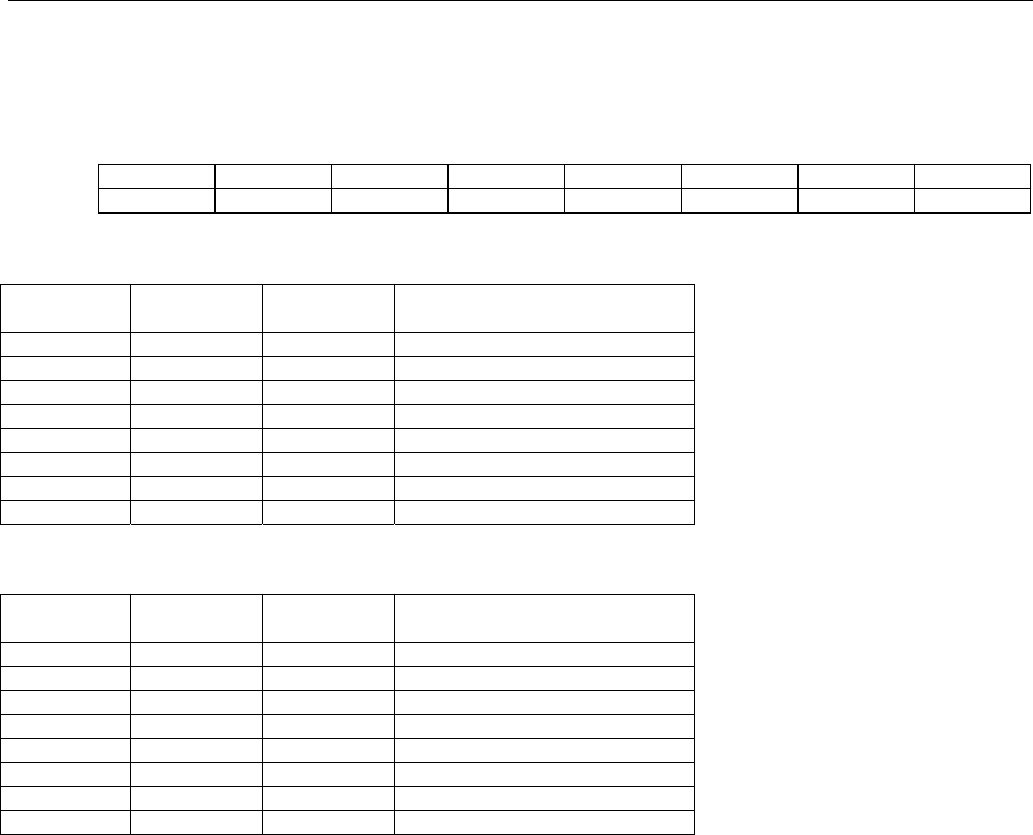

Bit # 7 6 5 4 3 2 1 0

Name — — TFLWM2 TFLWM1 TFLWM0 RFHWM2 RFHWM1 RFHWM0

Default 0 0 0 0 0 0 0 0

Bits 3 – 5: Transmit FIFO Low-Watermark Select (TFLWM0 to TFLWM2)

TFLWM2 TFLWM1 TFLWM0

Transmit FIFO Watermark

(bytes)

0 0 0 4

0 0 1 16

0 1 0 32

0 1 1 48

1 0 0 64

1 0 1 80

1 1 0 96

1 1 1 112

Bits 0 – 2: Receive FIFO High-Watermark Select (RFHWM0 to RFHWM2)

RFHWM2 RFHWM1 RFHWM0

Receive FIFO Watermark

(bytes)

0 0 0 4

0 0 1 16

0 1 0 32

0 1 1 48

1 0 0 64

1 0 1 80

1 1 0 96

1 1 1 112