DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

138 of 344

Register Name:

GL.TRQIE

Register Description:

Global Transmit Receive Queue Interrupt Enable

Register Address:

0Ah

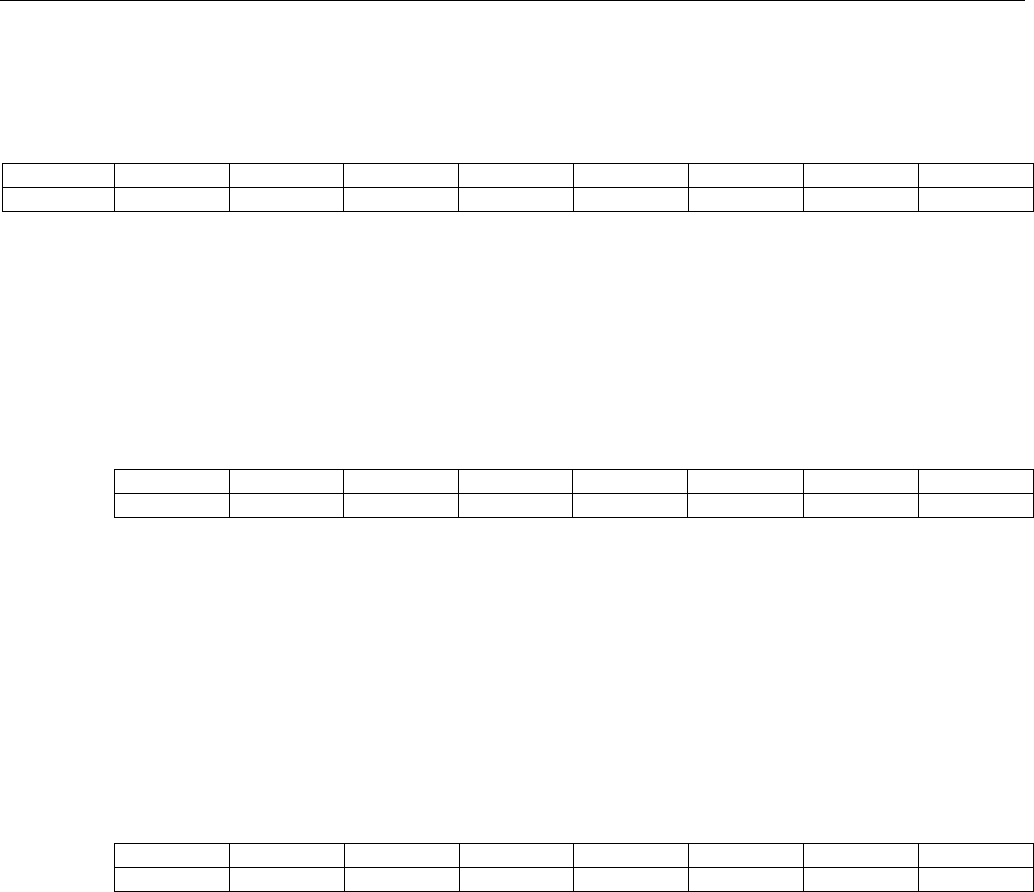

Bit # 7 6 5 4 3 2 1 0

Name - - - TQ1IE - - - RQ1IE

Default 0 0 0 0 0 0 0 0

Bit 4: Transmit Queue 1 Interrupt Enable (TQ1IE) Setting this bit to 1 enables an interrupt on TQ1IS.

Bit 0: Receive Queue 1 Interrupt Enable (RQ1IE) Setting this bit to 1 enables an interrupt on RQ1IS.

Register Name:

GL.TRQIS

Register Description:

Global Transmit Receive Queue Interrupt Status

Register Address:

0Bh

Bit # 7 6 5 4 3 2 1 0

Name - - - TQ1IS - - - RQ1IS

Default 0 0 0 0 0 0 0 0

Bit 4: Transmit Queue 1 Interrupt Enable (TQ1IS) If this bit is set to 1, the Transmit Queue 1 has interrupt status

event. Transmit queue events are transmit queue crossing thresholds and queue overflows.

Bit 0: Receive Queue 1 Interrupt Status (RQ1IS) If this bit is set to 1, the Receive Queue 1 has interrupt status

event. Receive queue events are transmit queue crossing thresholds and queue overflows.

Register Name:

GL.BIE

Register Description:

Global BERT Interrupt Enable

Register Address:

0Ch

Bit # 7 6 5 4 3 2 1 0

Name - - - - - - - BIE

Default 0 0 0 0 0 0 0 0

Bit 0: BERT Interrupt Enable (BIE) Setting this bit to 1 enables an interrupt on BIS.