DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

311 of 344

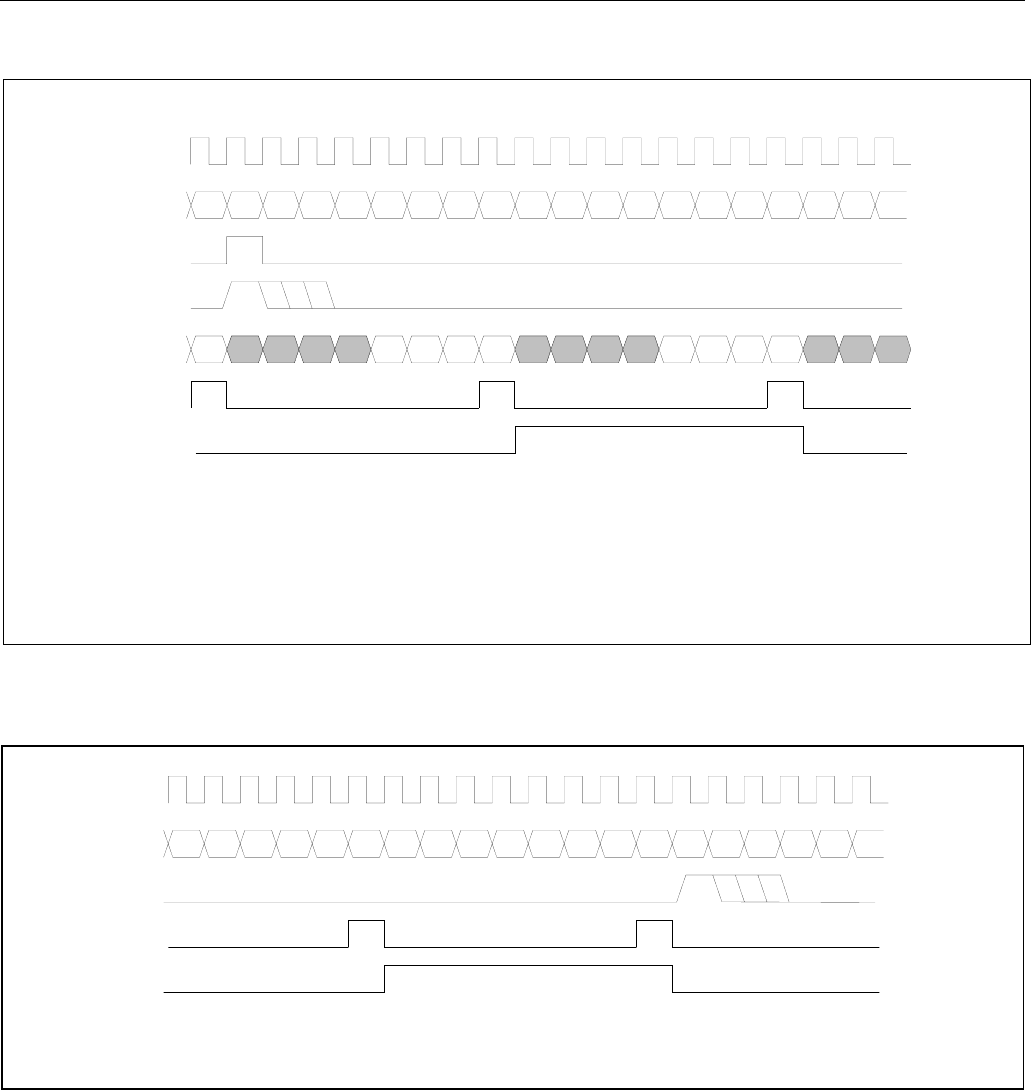

Figure 12-26. Transmit-Side Boundary Timing (Elastic Store Disabled)

LSB MSB LSB MSB

CHANNEL 1 CHANNEL 2

CHANNEL 1 CHANNEL 2

ABCD

TCLKT

TSERI

TSYNC

TSYNC

TSIG

TCHCLK

TCHBLK

1

2

3

Si 1 A Sa4 Sa5 Sa6 Sa7 Sa8

D

NOTE 1: TSYNC IS IN THE OUTPUT MODE (TR.IOCR1.1 = 1).

NOTE 2: TSYNC IS IN THE INPUT MODE (TR.IOCR1.1 = 0).

NOTE 3: TCHBLK IS PROGRAMMED TO BLOCK CHANNEL 2.

NOTE 5: THE SIGNALING DATA AT TSIG DURING CHANNEL 1 IS NORMALLY OVERWRITTEN IN THE TRANSMIT FORMATTER

WITH THE CAS MF ALIGNMENT NIBBLE (0000).

NOTE 6: SHOWN IS A TNAF FRAME BOUNDARY.

Figure 12-27. Transmit-Side Boundary Timing, TSYSCLK = 1.544MHz (Elastic Store

Enabled)

LSB F MSBLSB MSB

CHANNEL 1CHANNEL 24

TSYSCLK

TSERI

TSSYNC

TCHCLK

TCHBLK

CHANNEL 23

1

2

NOTE 1: THE F-BIT POSITION IN THE TSERI DATA IS IGNORED.

NOTE 2: TCHBLK IS PROGRAMMED TO BLOCK CHANNEL 24.