DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

306 of 344

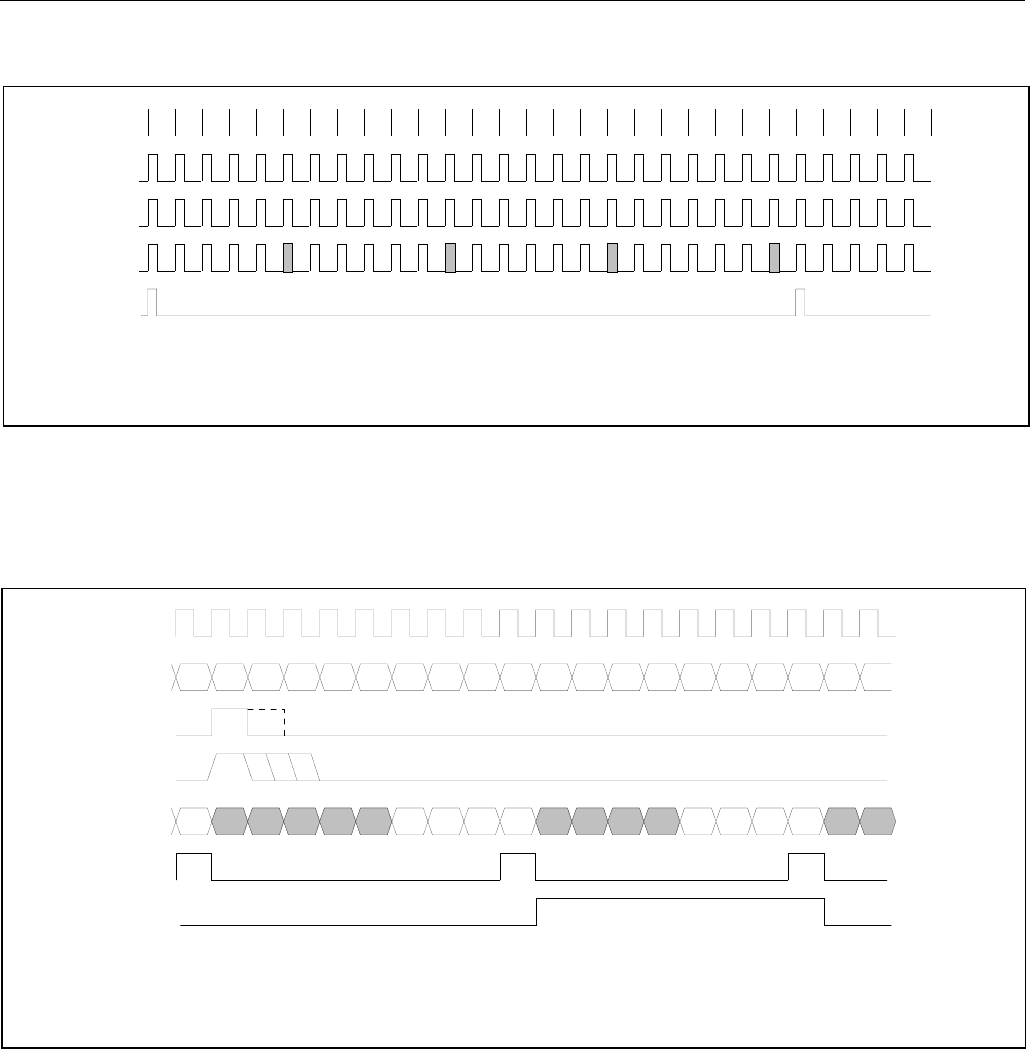

Figure 12-16. Transmit-Side ESF Timing

123456789101112

1

2

3

TSSYNC

FRAME#

TSYNC

TSYNC

TSYNC

13141516171819202122232412345

NOTE 1: TSYNC IN FRAME MODE (TR.IOCR1.2 = 0) AND DOUBLE-WIDE FRAME SYNC IS NOT ENABLED (TR.IOCR1.3 = 0).

NOTE 2: TSYNC IN FRAME MODE (TR.IOCR1.2 = 0) AND DOUBLE-WIDE FRAME SYNC IS ENABLED (TR.IOCR1.3 = 1).

NOTE 3: TSYNC IN MULTIFRAME MODE (TR.IOCR1.2 = 1).

Figure 12-17. Transmit-Side Boundary Timing (with Elastic Store Disabled)

LSB F MSB LSB MSB LSB MSB

CHANNEL 1 CHANNEL 2

CHANNEL 1 CHANNEL 2

ABC/AD/B ABC/AD/B

TCLKT

TSERI

TSYNC

TSYNC

TSIG

TCHCLK

TCHBLK

D/B

1

2

3

NOTE 1: TSYNC IS IN THE OUTPUT MODE (TR.IOCR1.1 = 1).

NOTE 2: TSYNC IS IN THE INPUT MODE (TR.IOCR1.1 = 0).

NOTE 3: TCHBLK IS PROGRAMMED TO BLOCK CHANNEL 2.