DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

334 of 344

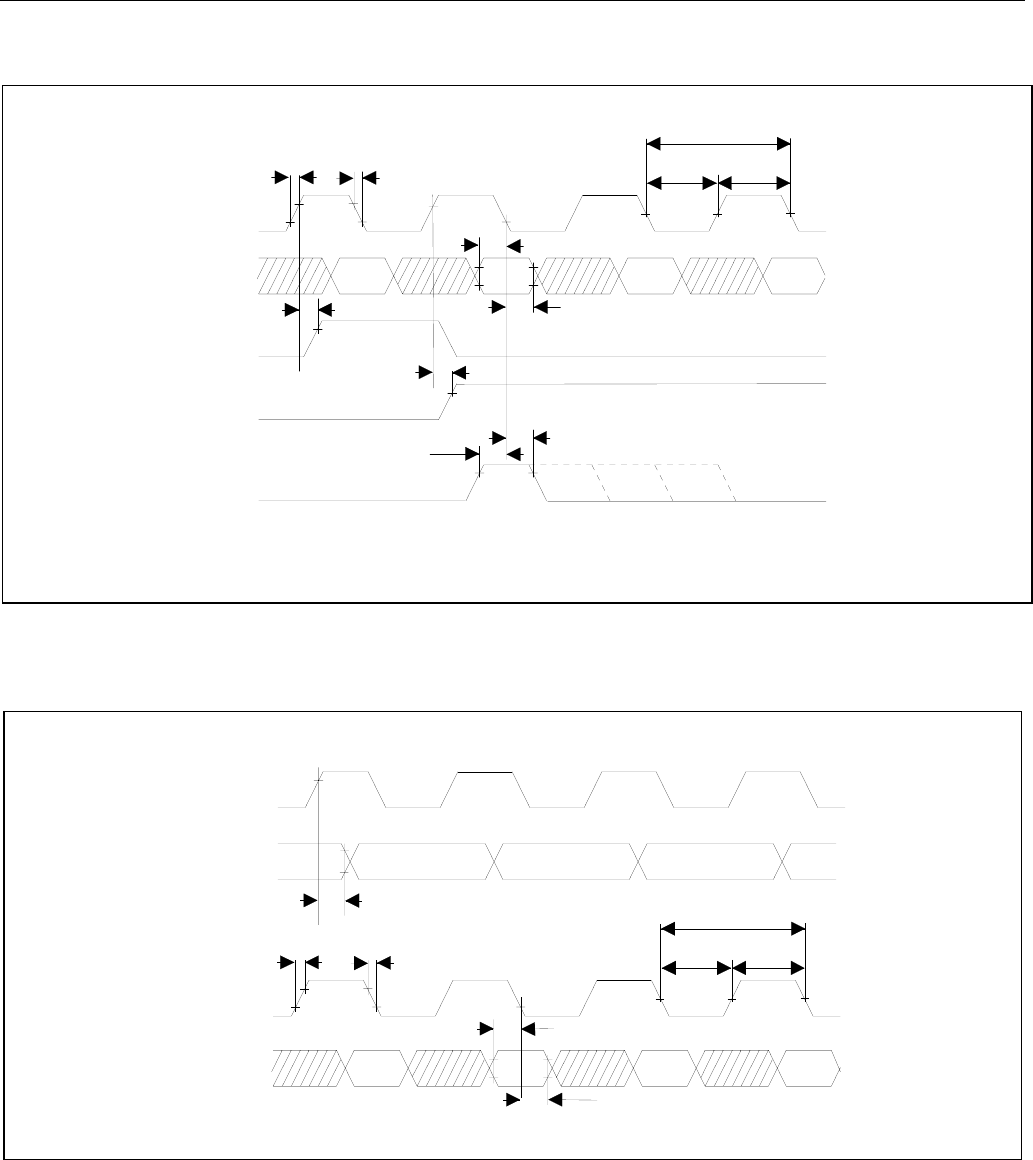

Figure 13-18. Transmit-Side Timing, Elastic Store Enabled

t

F

t

R

TSYSCLK

TSERI

TCHCLK

t

t

SL

t

SH

SP

TSSYNC

TCHBLK

t

D3

t

D3

t

t

t

SU

HD

SU

t

HD

NOTE 1: TSERI IS ONLY SAMPLED ON THE FALLING EDGE OF TSYSCLK WHEN THE TRANSMIT-SIDE ELASTIC STORE IS ENABLED.

NOTE 2: TCHCLK AND TCHBLK ARE SYNCHRONOUS WITH TSYSCLK WHEN THE TRANSMIT-SIDE ELASTIC STORE IS ENABLED.

Figure 13-19. Transmit Line Interface Timing

TDCLKO

TPOSO, TNEGO

t

DD

t

F

t

R

TDCLKI

TPOSI, TNEGI

t

t

LL

t

LH

LP

t

HD

t

SU