DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

80 of 344

10.7.3 Frames Out-of-Sync Count Register (TR.FOSCR)

In T1 mode, TR.FOSCR is used to count the number of multiframes that the receive synchronizer is out of sync.

This number is useful in ESF applications needing to measure the parameters loss-of-frame count (LOFC) and

ESF error events as described in AT&T publication TR54016. When TR.FOSCR is operated in this mode, it is not

disabled during receive loss-of-synchronization (RLOS = 1) conditions. TR.FOSCR has an alternate operating

mode whereby it counts either errors in the Ft framing pattern (in the D4 mode) or errors in the FPS framing pattern

(in the ESF mode). When TR.FOSCR is operated in this mode, it is disabled during receive loss-of-synchronization

(RLOS = 1) conditions.

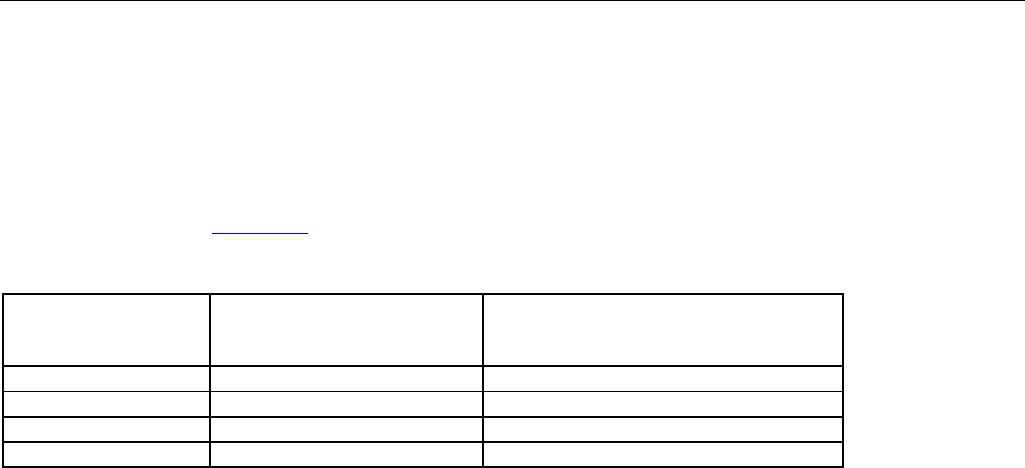

Table 10-8 shows what the FOSCR is capable of counting.

Table 10-8. T1 Frames Out-of-Sync Counting Arrangements

FRAMING MODE

(TR.T1RCR1.3)

COUNT MOS OR

F-BIT ERRORS

(TR.ERCNT.1)

COUNTED IN THE FOSCRs

D4 MOS Number of multiframes out-of-sync

D4 F-Bit Errors in the Ft pattern

ESF MOS Number of multiframes out-of-sync

ESF F-Bit Errors in the FPS pattern

In E1 mode, TR.FOSCR counts word errors in the FAS in time slot 0. This counter is disabled when RLOS is high.

FAS errors are not counted when the framer is searching for FAS alignment and/or synchronization at either the

CAS or CRC4 multiframe level. Since the maximum FAS word error count in a one-second period is 4000, this

counter cannot saturate.

The frames out-of-sync count register 1 (TR.FOSCR1) is the most significant word and TR.FOSCR2 is the least

significant word of a 16-bit counter that records frames out-of-sync.

10.7.4 E-Bit Counter (TR.EBCR)

This counter is only available in E1 mode. E-bit count register 1 (TR.EBCR1) is the most significant word and

TR.EBCR2 is the least significant word of a 16-bit counter that records far-end block errors (FEBE) as reported in

the first bit of frames 13 and 15 on E1 lines running with CRC4 multiframe. These count registers increment once

each time the received E-bit is set to 0. Since the maximum E-bit count in a one-second period is 1000, this

counter cannot saturate. The counter is disabled during loss-of-sync at either the FAS or CRC4 level; it continues

to count if loss-of-multiframe sync occurs at the CAS level.