DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

20 of 344

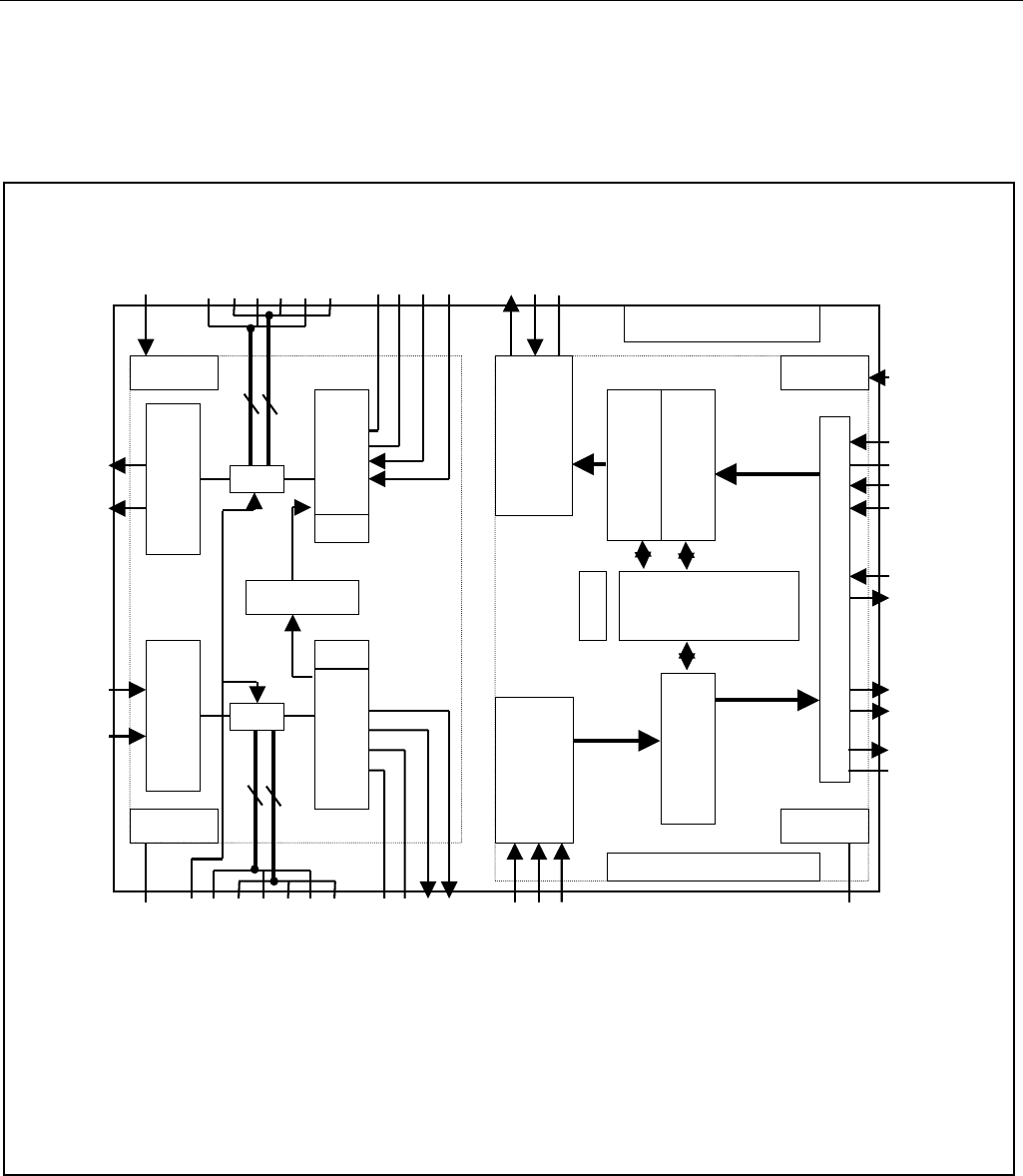

6 BLOCK DIAGRAMS

Figure 6-1. Main Block Diagram

TTIP

TRING

RTIP

RRING

SYSCLKI

(RMII MODE)

RXD[0:1]

RX_CLK

CRS_DV

RX_ERR

REF_CLK

REF_CLKO

TX_EN

TXD[0:1]

MDC

MDIO

MCLK

TDCLKI

TDCLKO

TPOSI

TPOSO

TNEGI

TNEGO

TCHBLK

TCHCLK

TCLKT

TSERI

TSERO

TCLKE

TDEN

JTAG Pin

s

LIUC

RDCLKI

RDCLKO

RPOSI

RPOSO

RNEGI

RNEGO

RCHBL

K

RCHCL

K

RCLKO

RSERO

RSERI

RCLKI

RDEN

TRANSMIT

LIU

RECEIVE

LIU

TRANSMIT

FRAMER

RECEIVIE

FRAMER

ETHERNET MAC

μP Port

SDRAM PORT

C

ST

C

S

A0-A9

D0-D7

W

R

R

D

I

NT

SDC

S

SRA

S

SCA

S

SW

E

SBA[0:1]

SDATA[0:32]

SDMASK[0:4

]

SDCL

K

JTAG Pins

ARBITER

CIR

CONTROLLER

PACKET

HDLC/X.86

PACKET

HDLC/X.86

ETHERNET

MAPPER

T1/E1/J1

TRANSCEIVER

TRANSMIT

SERIAL

PORT

RECEIVE

SERIAL

PORT

JTAG2 JTAG1

CLAD

MUX

MUX

CLAD

BERT

BERT

HDLC

HDLC

NOTE: SOME PINS NOT SHOWN. THE BLOCK IN THE DIAGRAM LABELED “T1/E1/J1 TRANSCEIVER” IS

DIVIDED INTO THREE FUNCTIONAL BLOCKS: LIU, FRAMER, AND BACKPLANE INTERFACE OUTLINED IN

THE FOLLOWING DIAGRAMS.