DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

229 of 344

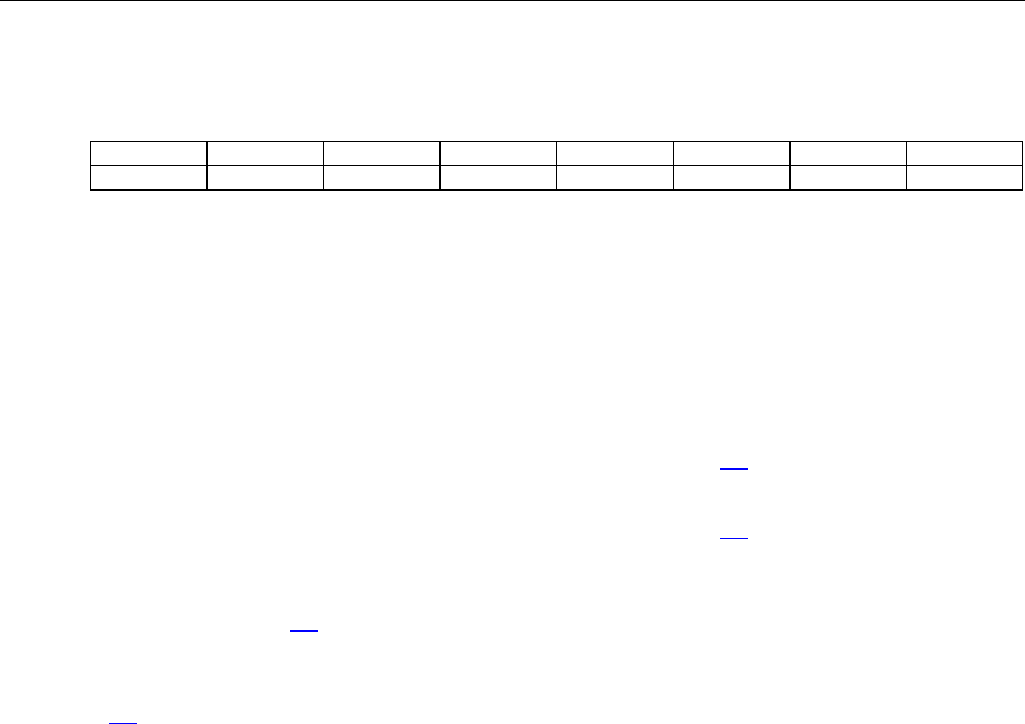

Register Name:

TR.SR9

Register Description:

Status Register 9

Register Address:

26h

Bit # 7 6 5 4 3 2 1 0

Name — BBED BBCO BEC0 BRA1 BRA0 BRLOS BSYNC

Default 0 0 0 0 0 0 0 0

Bit 6: BERT Bit-Error Detected (BED) Event (BBED). A latched bit that is set when a bit error is detected. The

receive BERT must be in synchronization for it to detect bit errors. Cleared when read.

Bit 5: BERT Bit-Counter Overflow Event (BBCO). A latched bit that is set when the 32-bit BERT bit counter

(BBC) overflows. Cleared when read and is not set again until another overflow occurs.

Bit 4: BERT Error-Counter Overflow (BECO) Event (BECO). A latched bit that is set when the 24-bit BERT error

counter (BEC) overflows. Cleared when read and is not set again until another overflow occurs.

Bit 3: BERT Receive All-Ones Condition (BRA1). A latched bit that is set when 32 consecutive 1s are received.

Allowed to be cleared once a 0 is received. This is a double interrupt bit (Section

9.7).

Bit 2: BERT Receive All-Zeros Condition (BRA0). A latched bit that is set when 32 consecutive 0s are received.

Allowed to be cleared once a 1 is received. This is a double interrupt bit (Section

9.7).

Bit 1: BERT Receive Loss-of-Synchronization Condition (BRLOS). A latched bit that is set whenever the

receive BERT begins searching for a pattern. Once synchronization is achieved, this bit remains set until read. This

is a double interrupt bit (Section

9.7).

Bit 0: BERT in Synchronization Condition (BSYNC). Set when the incoming pattern matches for 32 consecutive

bit positions. Refer to BSYNC in the TR.INFO2 register for a real-time version of this bit. This is a double interrupt

bit (Section

9.7).