DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

86 of 344

10.10 Per-Channel Idle Code Generation

Channel data can be replaced by an idle code on a per-channel basis in the transmit and receive directions. When

operated in the T1 mode, only the first 24 channels are used by the device, the remaining channels, CH25–CH32,

are not used.

The device contains a 64-byte idle code array accessed by the idle array address register (TR.IAAR) and the per-

channel idle code register (TR.PCICR). The contents of the array contain the idle codes to be substituted into the

appropriate transmit or receive channels. This substitution can be enabled and disabled on a per-channel basis by

the transmit-channel idle code-enable registers (TR.TCICE1–4) and receive-channel idle code-enable registers

(TR.RCICE1–4).

To program idle codes, first select a channel by writing to the TR.IAAR register. Then write the idle code to the

TR.PCICR register. For successive writes there is no need to load the TR.IAAR with the next consecutive address.

The TR.IAAR register automatically increments after a write to the TR.PCICR register. The auto increment feature

can be used for read operations as well. Bits 6 and 7 of the TR.IAAR register can be used to block write a common

idle code to all transmit or receive positions in the array with a single write to the TR.PCICR register. Bits 6 and 7

of the TR.IAAR register should not be used for read operations. TR.TCICE1–4 and TR.RCICE1–4 are used to

enable idle code replacement on a per-channel basis.

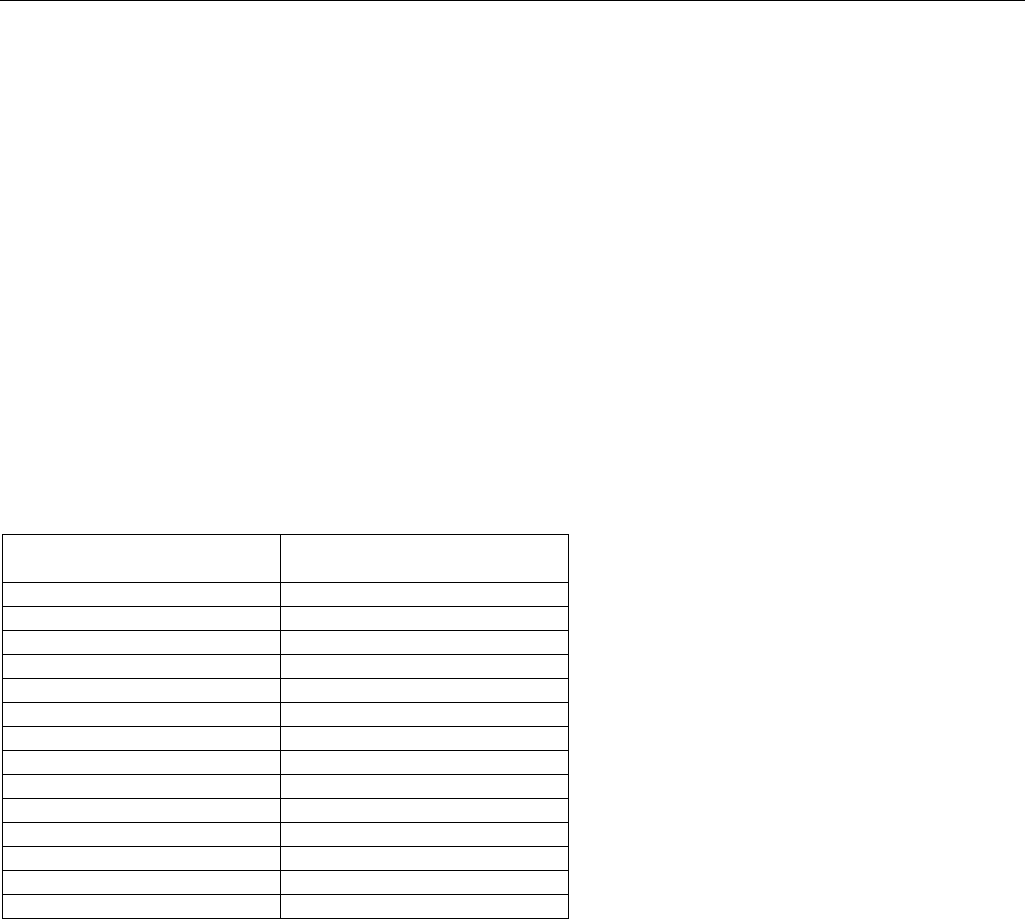

Table 10-10. Idle-Code Array Address Mapping

BITS 0 to 5 OF IAAR

REGISTER

MAPS TO CHANNEL

0 Transmit Channel 1

1 Transmit Channel 2

2 Transmit Channel 3

— —

— —

30 Transmit Channel 31

31 Transmit Channel 32

32 Receive Channel 1

33 Receive Channel 2

34 Receive Channel 3

— —

— —

62 Receive Channel 31

63 Receive Channel 32