DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

21 of 344

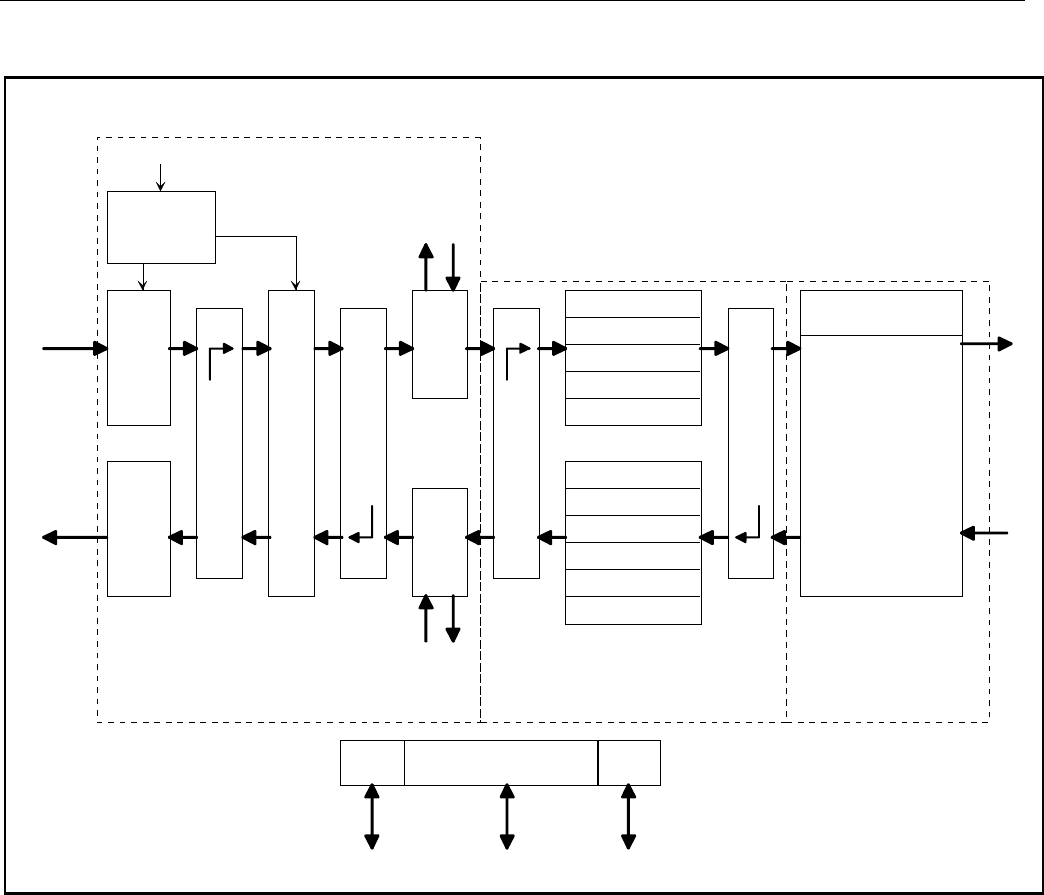

Figure 6-2. Block Diagram of T1/E1/J1 Transceiver

TX

LIU

CLOCK

ADAPTER

BACKPLANE

INTERFACE

CIRCUIT

HOST INTERFACE

T1/E1/J1

NETWORK

CLOCK

JTAG ESIB

RX

LIU

JITTER ATTENUATOR

LOCAL LOOPBACK

REMOTE LOOPBACK

FRAMER LOOPBACK

PAYLOAD LOOPBACK

MUX

MUX

EXTERNAL ACCESS

TO RECEIVE SIGNALS

EXTERNAL ACCESS

TO TRANSMIT SIGNALS

BACKPLANE

BACKPLANE

CLOCK SYNTH

LIU

FRAMER BACKPLANE

INTERFACE

SYNC

HDLCs

SINGALING

ALARM DET

FRAMER

CRC GEN

SINGALING

ALARM GEN

HDLCs

HDB3 / B8ZS

HDB3 / B8ZS