DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

303 of 344

RMII Receive data on RXD[1:0] is expected to be synchronous with the rising edge of the 50 MHz REF_CLK. The

data is only valid if CRS_DV is high. The external PHY asynchronously drives CRS_DV low during carrier loss.

Figure 12-9. RMII Receive Interface Functional Timing

RXD[1:0]

CRS_DV

REFCLK

P R E A M B L E F C S

12.3 Transceiver T1 Mode Functional Timing

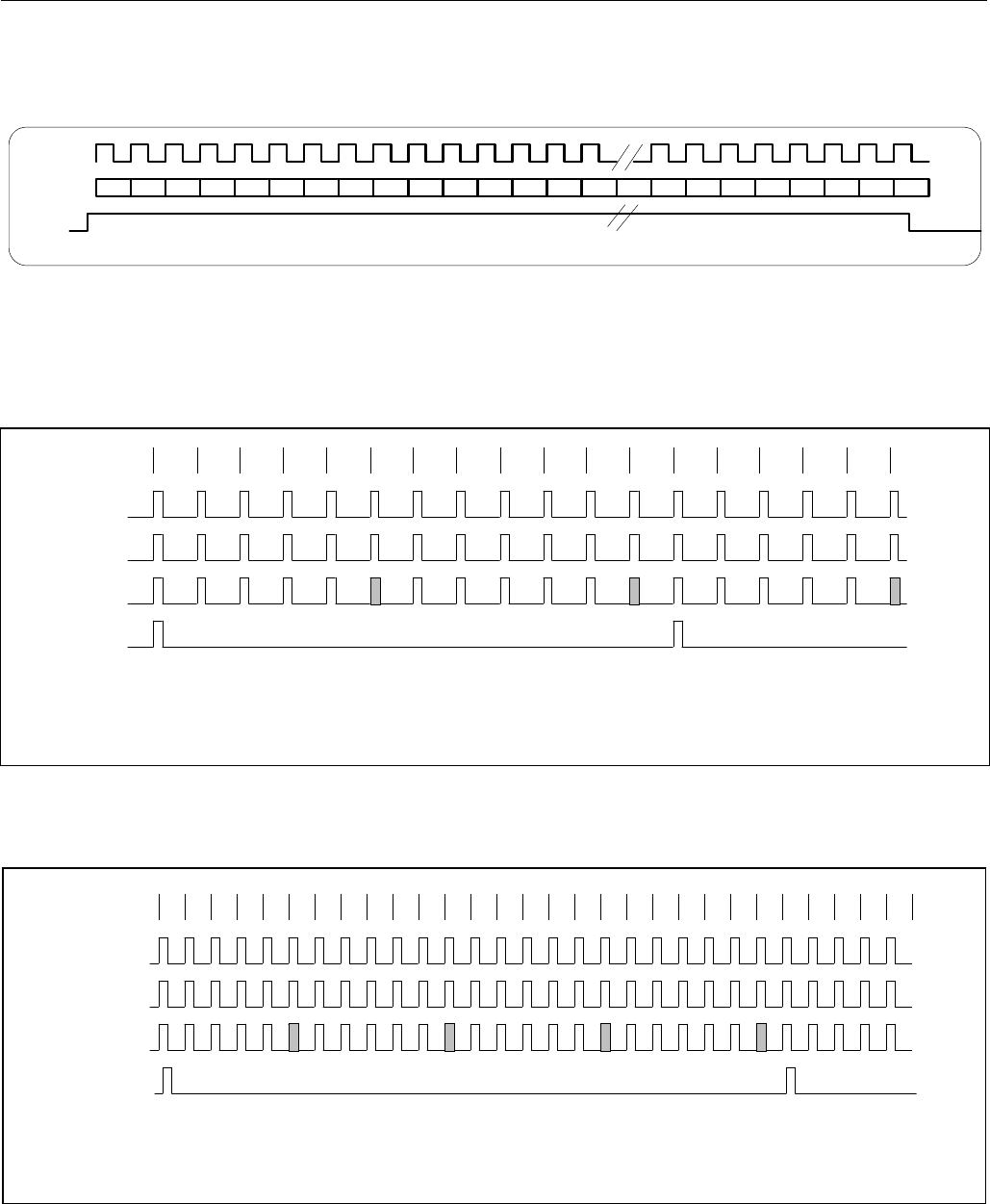

Figure 12-10. Receive-Side D4 Timing

FRAME#

1

2345678910111212345

3

RSYNC

1

RSYNC

RFSYNC

2

RSYNC

NOTE 1: RSYNC IN THE FRAME MODE (TR.IOCR1.5 = 0) AND DOUBLE-WIDE FRAME SYNC IS NOT ENABLED (TR.IOCR1.6 = 0).

NOTE 2: RSYNC IN THE FRAME MODE (TR.IOCR1.5 = 0) AND DOUBLE-WIDE FRAME SYNC IS ENABLED (TR.IOCR1.6 = 1).

NOTE 3: RSYNC IN THE MULTIFRAME MODE (TR.IOCR1.5 = 1).

Figure 12-11. Receive-Side ESF Timing

123456789101112

1

2

3

RFSYNC

FRAME#

RSYNC

RSYNC

RSYNC

13141516171819202122232412345

NOTE 1: RSYNC IN FRAME MODE (TR.IOCR1.4 = 0) AND DOUBLE-WIDE FRAME SYNC IS NOT ENABLED (TR.IOCR1.6 = 0).

NOTE 2: RSYNC IN FRAME MODE (TR.IOCR1.4 = 0) AND DOUBLE-WIDE FRAME SYNC IS ENABLED (TR.IOCR1.6 = 1).

NOTE 3: RSYNC IN MULTIFRAME MODE (TR.IOCR1.4 = 1).