DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

278 of 344

Register Name:

TR.RFDL (TR.BOCC.4 = 1)

Register Description:

Receive FDL Register

Register Address:

C0h

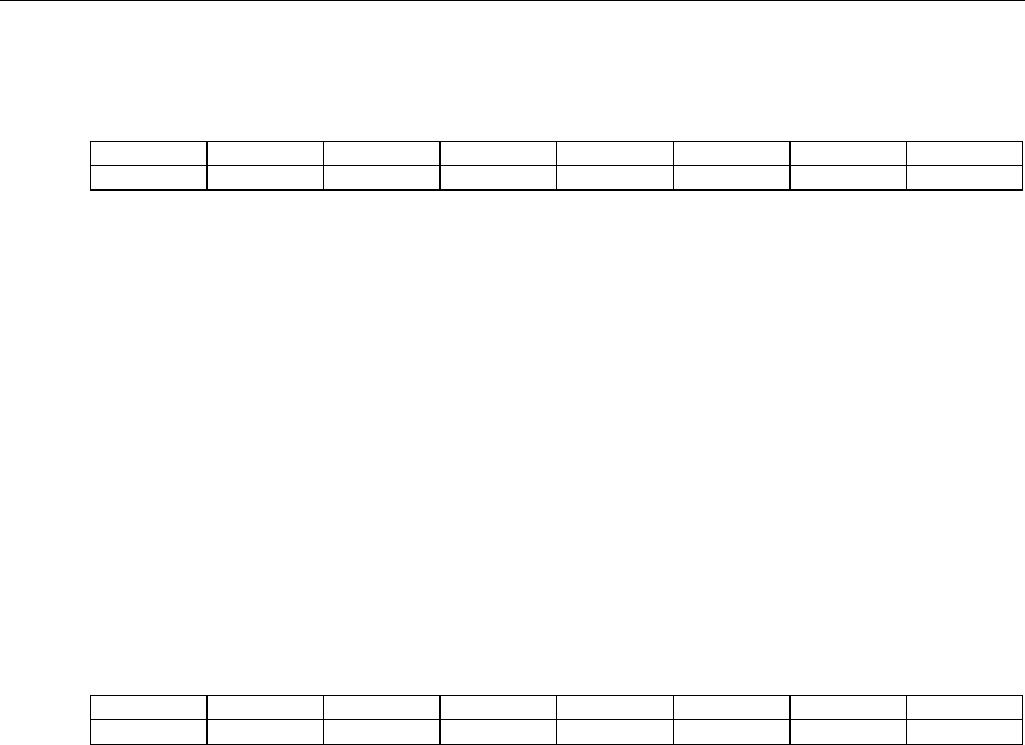

Bit # 7 6 5 4 3 2 1 0

Name — — RBOC5 RBOC4 RBOC3 RBOC2 RBOC1 RBOC0

Default 0 0 0 0 0 0 0 0

RFDL register bit definitions when TR.BOCC.4 = 1:

Bit 5: BOC Bit 5 (RBOC5)

Bit 4: BOC Bit 4 (RBOC4)

Bit 3: BOC Bit 3 (RBOC3)

Bit 2: BOC Bit 2 (RBOC2)

Bit 1: BOC Bit 1 (RBOC1)

Bit 0: BOC Bit 0 (RBOC0)

Register Name:

TR.RFDL (TR.BOCC.4 = 0)

Register Description:

Receive FDL Register

Register Address:

C0h

Bit # 7 6 5 4 3 2 1 0

Name RFDL7 RFDL6 RFDL5 RFDL4 RFDL3 RFDL2 RFDL1 RFDL0

Default 0 0 0 0 0 0 0 0

The receive FDL register (TR.RFDL) reports the incoming FDL or the incoming Fs bits. The LSB is received first.

Bit 7: Receive FDL Bit 7 (RFDL7). MSB of the received FDL code.

Bit 6: Receive FDL Bit 6 (RFDL6)

Bit 5: Receive FDL Bit 5 (RFDL5)

Bit 4: Receive FDL Bit 4 (RFDL4)

Bit 3: Receive FDL Bit 3 (RFDL3)

Bit 2: Receive FDL Bit 2 (RFDL2)

Bit 1: Receive FDL Bit 1 (RFDL1)

Bit 0: Receive FDL Bit 0 (RFDL0). LSB of the received FDL code.