DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

40 of 344

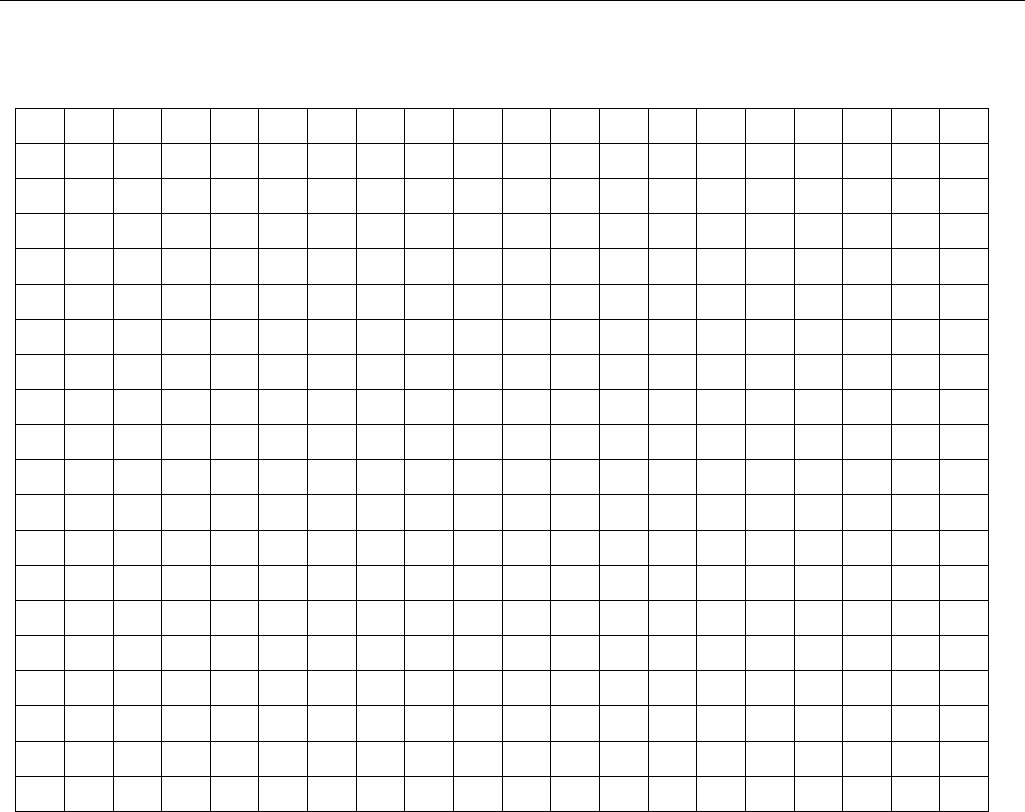

Figure 7-1. 256-Ball BGA Pinout

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

A

RCHBLK TCHBLK RFSYNC TDATA TSSYNC JTCLK2 JTCLK1

RST

N.C.

INT CS

D6 D3 D0 VSS A6 A3 A0 REF_CLK

REF_

CLKO

B

BPCLK LIUC TPOSI TSIG RCL JTDI2 JTDO1

JTRST2

JTMS2 VDD1.8

RD/DS

D7 D4 D1 VDD1.8 A7 A4 A1

MODEC

[0]

MODEC

[1]

C

TSYNC TDCLKO TNEGI TSTRST JTDO2 N.C.

JTRST1

JTMS1 JTDI1 VSS

WR/RW

VDD1.8 D5 D2 A9 A8 A5 A2 MDC MDIO

D

TDCLKI TCLKT TNEGO TESO

TDEN/

TBSYNC

N.C.

CST

VSS VSS VSS DVDD DVDD DVDD DVDD DVDD DVDD DVDD VSS VSS VDD3

E

TPOSO TSERO TSERI TSYSCLK DVDD VSS

TXD

[3]

TXD

[2]

F

TCLKE RCLKI VDD1.8 RSYSCLK VDD3

TXD

[1]

TXD

[0]

TX_EN

G

TCHCLK RCHCLK RCLKO RSYNC VDD3 VDD3 RMIIMIIS

DCE

DTES

H

RSERI RSERO RDATA MCLK VDD3 QOVF TX_CLK VSS

J

RVSS RVSS RPOSI XTALD VDD3 VDD1.8 VSS VDD1.8

K

RTIP RVSS RVDD 8XCLK VDD3 RX_ERR RX_DV VSS

L

RVDD RVSS RSIG RNEGI VDD3

RXD

[0]

RXD

[1]

RXD

[2]

M

RRING RVSS RDCLKO RDCLKI VDD3

RXD

[3]

RX_CRS /

CRS_DV

RX_CLK

N

RLOS/

LTC

RNEGO RPOSO DVSS VDD3 COL_DEt VSS VSS

P

TVSS

RDEN/

RBSYNC

RSIGF DVSS VDD3 VDD1.8 VDD1.8 VSS

R

TTIP TTIP TVSS DVSS VDD3 VDD3 VDD1.8 VDD1.8

T

TRING TRING TVSS DVSS VDD3 VDD3

SDATA

[25]

SDATA

[26]

U

TVDD TVSS RMSYNC VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VSS VDD3 VSS

SDATA

[22]

SDATA

[24]

V

SDATA

[13]

SDATA

[11]

SDATA

[12]

SDATA

[10]

SDATA

[6]

SDATA

[8]

SDMASK

[1]

SYSCLKI VDD1.8

SDCS

SBA

[1]

SDA

[8]

SDA

[5]

SDA

[10]

SDMASK

[3]

SDMASK

[2]

SDATA

[29]

SDATA

[18]

SDATA

[20]

VSS

W

SDATA

[15]

SDATA

[0]

SDATA

[14]

SDATA

[9]

SDATA

[5]

SDATA

[7]

SCAS

VSS

SRAS SWE

SDA

[11]

SDA

[1]

SDA

[6]

SDA

[0]

SDA

[3]

SDATA

[31]

SDATA

[30]

VSS

SDATA

[28]

SDATA

[23]

Y

VSS

SDATA

[2]

SDATA

[4]

SDATA

[1]

SDATA

[3]

SDMASK

[0]

VSS SDCLKO VDD1.8

SDA

[9]

SBA

[0]

SDA

[7]

VDD1.8

SDA

[4]

SDA

[2]

SDATA

[16]

SDATA

[17]

SDATA

[27]

SDATA

[19]

SDATA

[21]