DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

60 of 344

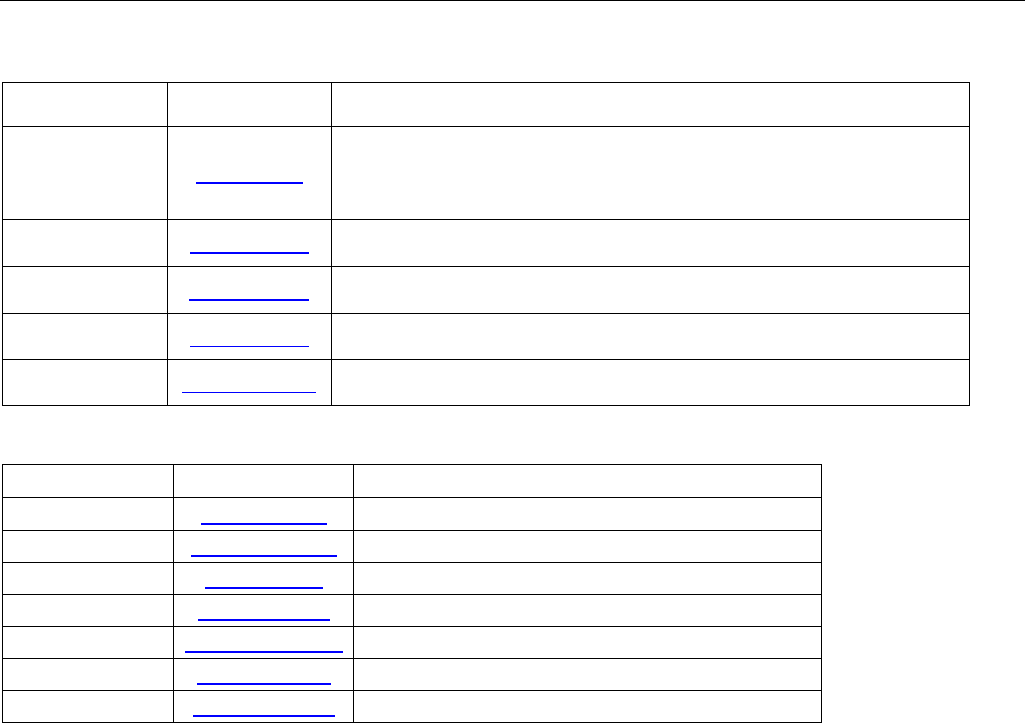

Table 9-6. MAC Control Registers

ADDRESS REGISTER DESCRIPTION

0000h-0003h SU.MACCR

MAC Control Register. This register is used for programming full

duplex, half duplex, promiscuous mode, and back-off limit for half

duplex. The transmit and receive enable bits must be set for the MAC

to operate.

0014h-0017h SU.MACMIIA

MAC MII Management (MDIO) Address Register. The address for

PHY access through the MDIO interface.

0018h-001Bh SU.MACMIID

MAC MII (MDIO) Data Register. Data to be written to (or read from)

the PHY through MDIO interface.

001Ch-001Fh SU.MACFCR MAC Flow Control Register

0100h-0103h SU.MMCCTRL MAC MMC Control Register. Bit 0 for resetting the status counters.

Table 9-7. MAC Status Registers

ADDRESS REGISTER DESCRIPTION

0200h-0203h SU.RxFrmCtr All frames received counter.

0204h-0207h SU.RxFrmOkCtr Number of received frames that are good.

0300h-0303h SU.TxFrmCtr Number of frames transmitted.

0308h-030Bh SU.TxBytesCtr Number of bytes transmitted.

030Ch-030Fh SU.TxBytesOkCtr Number of bytes transmitted with good frames.

0334h-0337h SU.TxFrmUndr Transmit FIFO underflow counter.

0338h-033Bh SU.TxBdFrmCtr Transmit number of frames aborted.