DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

336 of 344

14 JTAG INFORMATION

The DS33R11 contains two JTAG ports. Port 1 is for the Ethernet Mapper, and Port 2 is for the T1/E1/J1

Transceiver. Because of this, this device requires special consideration during JTAG test design. For more

information on performing JTAG testing using this device, go to www.maxim-ic.com/support

.

The device supports the standard instruction codes SAMPLE:PRELOAD, BYPASS, and EXTEST. Optional public

instructions included are HIGHZ, CLAMP, and IDCODE. See Table 14-1

. The DS33R11 contains the following as

required by IEEE 1149.1 Standard Test Access Port and Boundary Scan Architecture.

Test Access Port (TAP)

TAP Controller

Instruction Register

Bypass Register

Boundary Scan Register

Device Identification Register

The Test Access Port has the necessary interface pins: JTRST, JTCLK, JTMS, JTDI, and JTDO. See the pin

descriptions for details. Refer to IEEE 1149.1-1990, IEEE 1149.1a-1993, and IEEE 1149.1b-1994 for details about

the Boundary Scan Architecture and the Test Access Port.

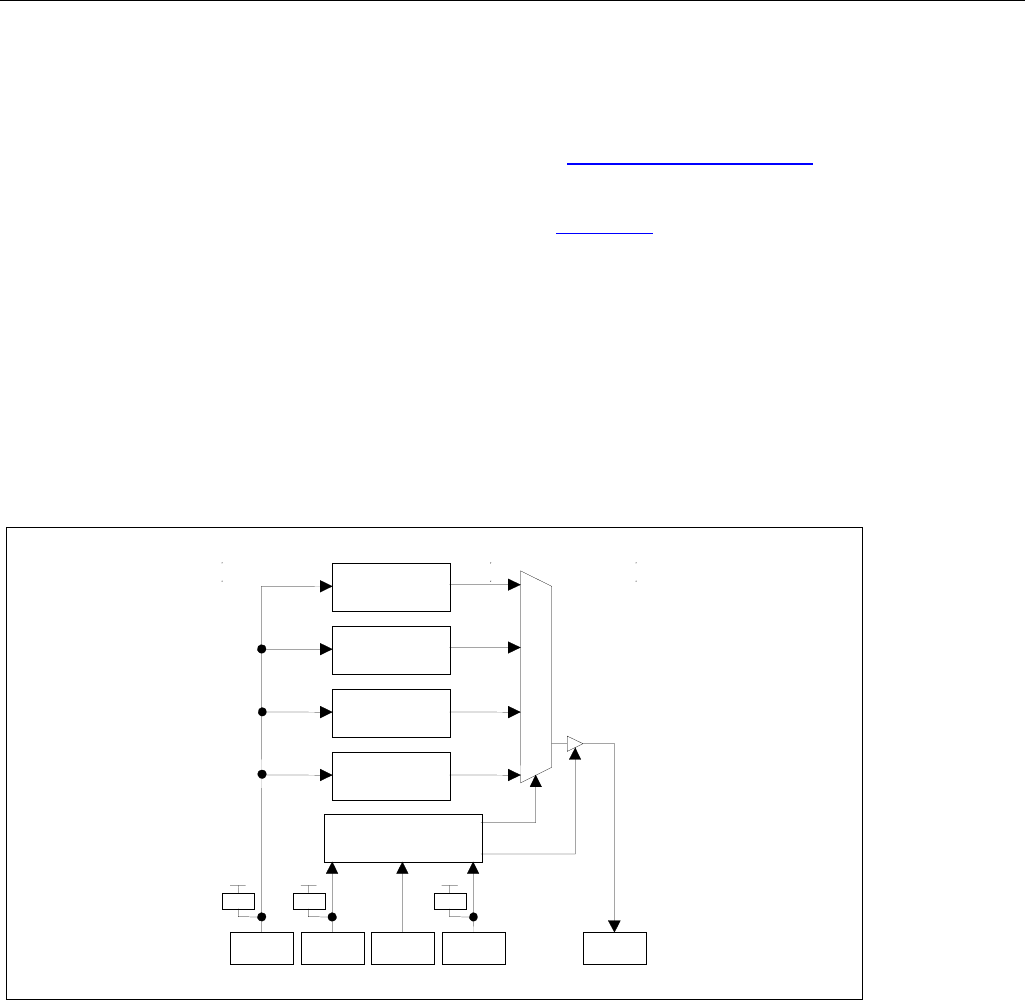

Figure 14-1. JTAG Functional Block Diagram

Boundary Scan

Register

Identification

Register

B

yp

ass

Register

Instruction

Register

Test Access Port

Controller

Mux

Select

Tri-State

JTDI

10K

JTMS

10K

JTCLK

J

TRST

10K

JTDO