DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

38 of 344

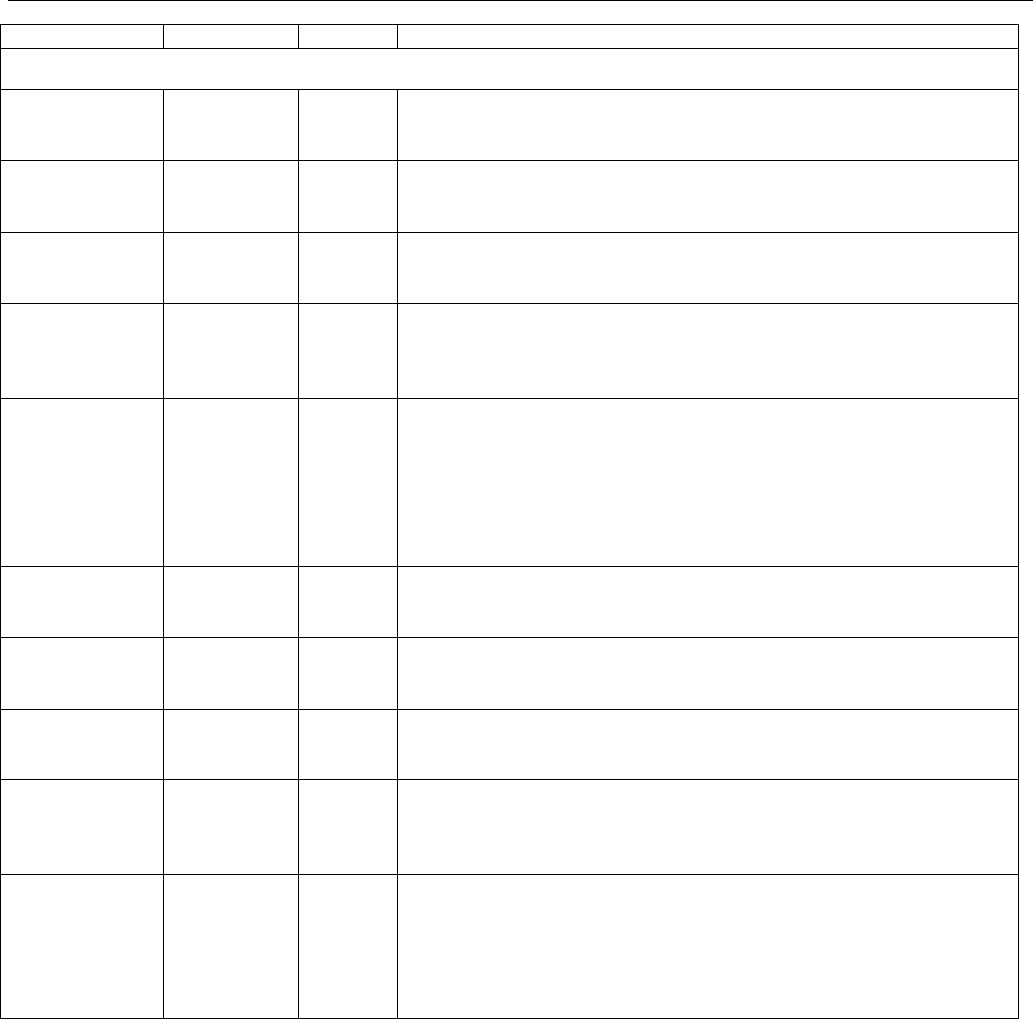

NAME PIN TYPE FUNCTION

JTAG INTERFACE

JTCLK1 A7 Ipu

JTAG Clock 1 for the Ethernet Mapper: This signal is used to

shift data into JTDI1 on the rising edge and out of JTDO1 on the

falling edge.

JTDI1 C9 Ipu

JTAG Data In 1 for the Ethernet Mapper: Test instructions and

data are clocked into this pin on the rising edge of JTCLK1. This

pin has a 10kΩ pullup resistor.

JTDO1 B7 Oz

JTAG Data Out 1 for the Ethernet Mapper: Test instructions and

data are clocked out of this pin on the falling edge of JTCLK1. If not

used, this pin should be left unconnected.

JTMS1 C8 Ipu

JTAG Mode Select 1 for the Ethernet Mapper: This pin is

sampled on the rising edge of JTCLK1 and is used to place the test

access port into the various defined IEEE 1149.1 states. This pin

has a 10kΩ pullup resistor.

JTRST1

C7 Ipu

JTAG Reset 1 for the Ethernet Mapper: JTRST1 is used to

asynchronously reset the test access port controller. After power

up, a rising edge on JTRST1 will reset the test port and cause the

device I/O to enter the JTAG DEVICE ID mode. Pulling JTRST1

low restores normal device operation. JTRST1 is pulled HIGH

internally via a 10kΩ resistor operation. If boundary scan is not

used, this pin should be held low.

JTCLK2 A6 Ipu

JTAG Clock 2 for the T1/E1/J1 Transceiver: This signal is used

to shift data into JTDI1 on the rising edge and out of JTDO1 on the

falling edge.

JTDI2 B6 Ipu

JTAG Data In 2 for the T1/E1/J1 Transceiver: Test instructions

and data are clocked into this pin on the rising edge of JTCLK2.

This pin has a 10kΩ pullup resistor.

JTDO2 C5 Oz

JTAG Data Out 2 for the T1/E1/J1 Transceiver: Test instructions

and data are clocked out of this pin on the falling edge of JTCLK2.

If not used, this pin should be left unconnected.

JTMS2 B9 Ipu

JTAG Mode Select 2 for the T1/E1/J1 Transceiver: This pin is

sampled on the rising edge of JTCLK2 and is used to place the

test-access port into the various defined IEEE 1149.1 states. This

pin has a 10kΩ pullup resistor.

JTRST2

B8 Ipu

JTAG Reset 2 for the T1/E1/J1 Transceiver: JTRST2 is used to

asynchronously reset the test access port controller. After power-

up, JTRST2 must be toggled from low to high. This action will set

the device into the JTAG DEVICE ID mode. Normal device

operation is restored by pulling JTRST2 low. JTRST2 is pulled HIGH

internally via a 10kΩ resistor operation.