DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

64 of 344

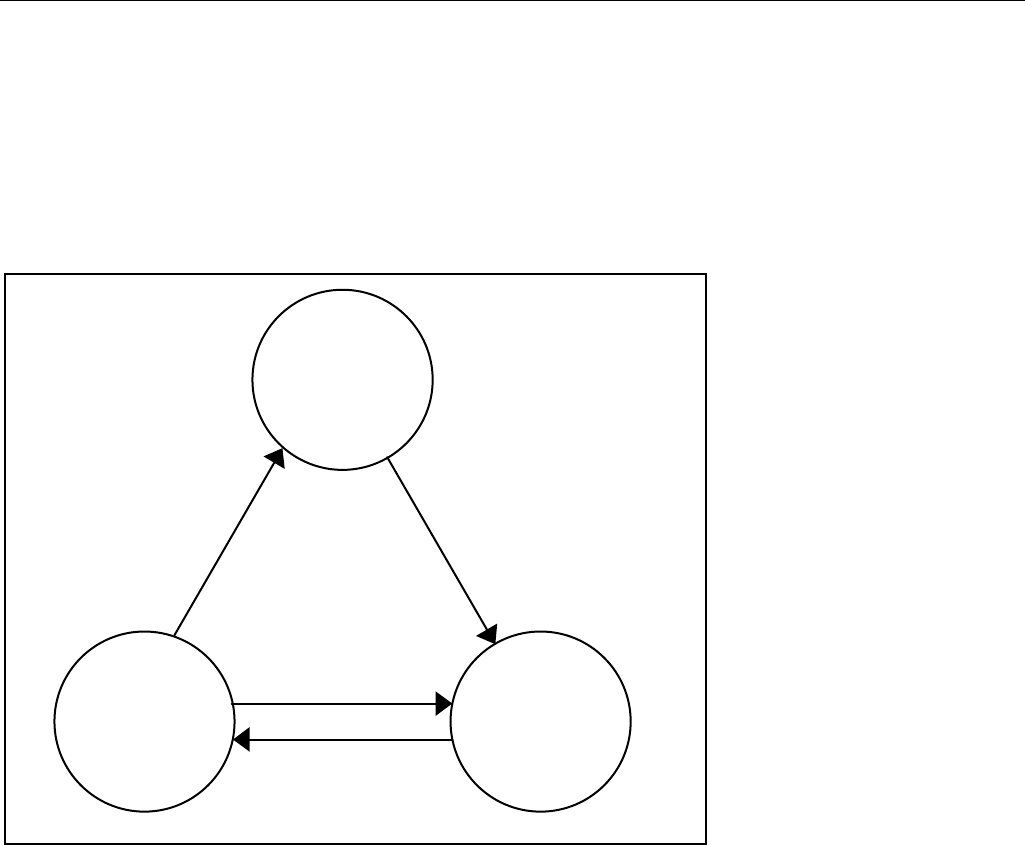

9.16.2 Repetitive Pattern Synchronization

Repetitive pattern synchronization synchronizes the receive pattern generator to the incoming repetitive pattern.

The receive pattern generator is synchronized by searching each incoming data stream bit position for the

repetitive pattern, and then checking the next 32 data stream bits. Synchronization is achieved if all 32 bits match

the incoming pattern. If at least sis incoming bits in the current 64-bit window do not match the receive PRBS

pattern generator, automatic pattern resynchronization is initiated. Automatic pattern resynchronization can be

disabled.

Figure 9-10. Repetitive Pattern Synchronization State Diagram

Sync

MatchVerify

1 bit error

Pattern Matches

3

2

b

i

t

s

w

i

t

h

o

u

t

e

rro

rs

6

o

f

6

4

b

i

t

s

w

it

h

e

r

r

o

rs

9.16.3 Pattern Monitoring

Pattern monitoring monitors the incoming data stream for Out Of Synchronization (OOS) condition, bit errors, and

counts the incoming bits. An OOS condition is declared when the synchronization state machine is not in the

“Sync” state. An OOS condition is terminated when the synchronization state machine is in the “Sync” state.

Bit errors are determined by comparing the incoming data stream bit to the receive pattern generator output. If they

do not match, a bit error is declared, and the bit error and bit counts are incremented. If they match, only the bit

count is incremented. The bit count and bit error count are not incremented when an OOS condition exists.

9.16.4 Pattern Generation

Pattern Generation generates the outgoing test pattern, and passes it onto Error Insertion. The transmit pattern

generator is a 32-bit shift register that shifts data from the least significant bit (LSB) or bit 1 to the most significant

bit (MSB) or bit 32. The input to bit 1 is the feedback. For a PRBS pattern (generating polynomial x

n

+ x

y

+ 1), the

feedback is an XOR of bit n and bit y. For a repetitive pattern (length n), the feedback is bit n. The values for n and

y are individually programmable. The output of the receive pattern generator is the feedback. If QRSS is enabled,

the feedback is an XOR of bits 17 and 20, and the output is forced to one if the next 14 bits are all zeros. QRSS is

programmable (on or off). For PRBS and QRSS patterns, the feedback is forced to one if bits 1 through 31 are all

zeros. When a new pattern is loaded, the pattern generator is loaded with a pattern value before pattern generation

starts. The pattern value is programmable (0 – 2

n

- 1). When PRBS and QRSS patterns are generated the seed

value is all ones.