DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

312 of 344

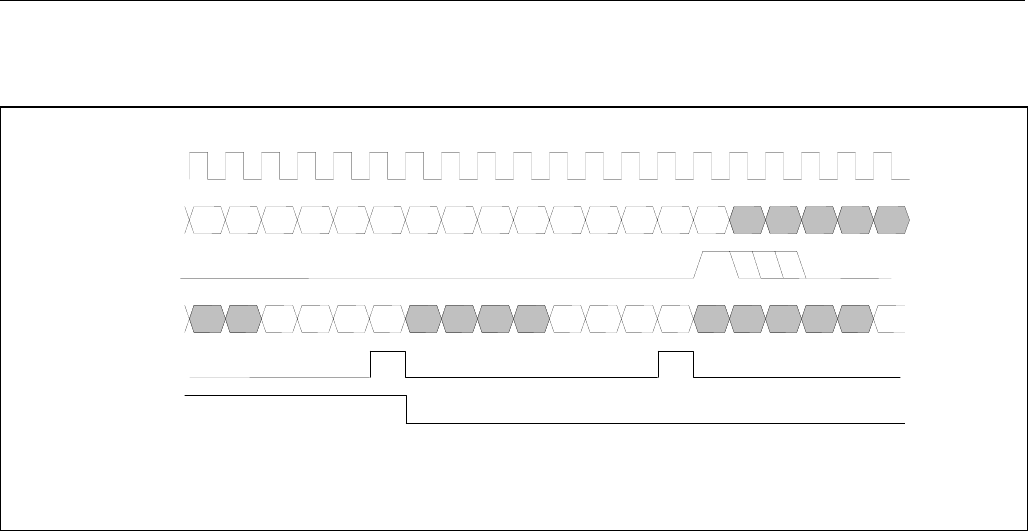

Figure 12-28. Transmit-Side Boundary Timing, TSYSCLK = 2.048MHz (Elastic Store

Enabled)

LSB

F

LSB MSB

CHANNEL 1 CHANNEL 32

A

B C D

A

B

TSYSCLK

TSERI

TSSYNC

TSIG

TCHCLK

TCHBL

K

CHANNEL 31

A

CHANNEL 31 CHANNEL 32 CHANNEL 1

1

4

C D

NOTE 1: TCHBLK IS PROGRAMMED TO BLOCK CHANNEL 31.